doi: 10.11835/j.issn.1000-582X.2024.207

引用格式:赵柯,蒋华平,汤磊,等.抑制碳化硅 MOSFET 阈值电压漂移的驱动电路[J].重庆大学学报,2025,48(9): 50-56.

# 抑制碳化硅 MOSFET 阈值电压漂移的驱动电路

赵 柯,蒋华平,汤 磊,钟笑寒,谢宇庭,胡浩伟,肖念磊,黄诣涵,刘 立

(重庆大学输变电装备技术全国重点实验室,重庆 400044)

**摘要:**碳化硅金属-氧化物-半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor, MOSFET)的阈值电压漂移严重影响了其在应用中的可靠性。针对该问题,文中总结了碳化硅 MOSFET 阈值电压漂移的特点与现有的理论模型,提出抑制阈值电压漂移的驱动方法与驱动电路。该驱动电路通过引入中间电平的方式,将被控器件关断动态过程与关断稳态后的栅极电压区分开来,以此来达到降低碳化硅 MOSFET 的阈值电压漂移量的目的,同时还可以保留负栅极关断电压的优势。搭建了实验平台来验证该驱动电路对碳化硅 MOSFET 阈值电压漂移的抑制效果,结果表明,在文中的实验条件下该驱动电路相比于传统的驱动方式阈值电压漂移量降低了 37%。

**关键词:**碳化硅;金属-氧化物-半导体场效应晶体管器件;阈值电压;栅极驱动器

中图分类号:TN 386 文献标志码:A 文章编号:1000-582X(2025)09-050-07

## Driving circuit for suppressing threshold voltage drift in silicon carbide MOSFETs

ZHAO Ke, JIANG Huaping, TANG Lei, ZHONG Xiaohan, XIE Yuting, HU Haowei,

XIAO Nianlei, HUANG Yihan, LIU Li

(State Key Laboratory of Power Transmission Equipment Technology, Chongqing University,

Chongqing 400044, P. R. China)

**Abstract:** Threshold voltage drift in silicon carbide metal-oxide-semiconductor field-effect transistors (MOSFETs) poses a significant challenge to device reliability in practical applications. This paper reviews the characteristics and existing theoretical models of threshold voltage drift in silicon carbide MOSFETs and proposes a novel gate driving method and circuit to mitigate this issue. The proposed circuit differentiates the device's turn-off dynamic process from the post turn-off gate voltage by introducing an intermediate voltage level, thereby effectively suppressing threshold voltage drift while retaining the benefits of a negative gate turn-off voltage. An experimental platform was constructed to evaluate the proposed driving circuit. Experimental results indicate that, under the specified conditions, the new circuit reduces threshold voltage drift by 37% compared to conventional driving methods.

**Keywords:** silicon carbide; metal-oxide-semiconductor field-effect transistor (MOSFET); threshold voltage; gate driver

收稿日期:2023-10-05 网络出版日期:2024-04-17

作者简介:赵柯(1998—),男,硕士研究生,主要从事碳化硅器件可靠性研究,(E-mail)202111021036@stu.cqu.edu.cn。

通信作者:蒋华平,男,研究员,博士生导师,(E-mail)Huaping.Jiang@cqu.edu.cn。

与传统的硅基器件相比,碳化硅金属-氧化物-半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor, MOSFET)具备低开关损耗和高工作频率等优势<sup>[1-3]</sup>,能满足电动汽车驱动、光伏逆变器等应用侧的需求<sup>[4-6]</sup>。然而,人们在应用中发现碳化硅MOSFET的栅极氧化层中存在高密度陷阱,导致器件出现阈值电压漂移现象<sup>[7-9]</sup>。阈值电压增大会导致器件导通电阻的增加,从而增加器件的导通损耗和发热量;阈值电压减小则会增加器件误触发的风险,从而降低器件的可靠性<sup>[10]</sup>。

现有研究表明,只有在碳化硅MOSFET栅极上施加正负交替的双极性电压应力,并且关断电压要低于某个临界负压时器件才会发生明显的阈值漂移现象;在器件栅极上只施压正压或只施加负压应力,则不会引起明显的阈值电压漂移<sup>[11-12]</sup>。典型工况中一般都在器件栅极上施加双极性电压应力,因为负栅极关断电压不仅可以提升器件的关断速度,而且还可以提高器件的抗串扰能力,降低误导通的风险<sup>[13-14]</sup>。

有学者提出“局部电场模型”来解释碳化硅MOSFET阈值电压漂移的物理机理。在碳化硅MOSFET栅极承受负电压应力的状态下,栅极氧化层陷阱会捕获空穴并形成局部电场,当栅极从负电压切换为正电压时,该局部电场来不及完全消失,从而导致更多的电子被氧化层陷阱捕获造成器件阈值电压增大(正漂),栅极从正电压切换为负电压的过程类似。Jiang等<sup>[15]</sup>用该模型解释了器件阈值电压漂移会随栅极电压变化率增大而增大的原因。从实验结果看,主流厂商的碳化硅MOSFET在双极性栅极电压应力下总是呈正漂现象<sup>[11-12,15]</sup>,故可以认为栅极电压从负压切换为正压过程中造成大量电子被捕获是占主导作用的,因为这部分被捕获的电子更加难以释放,从而导致器件的阈值电压增大。

综上所述,结合碳化硅MOSFET阈值电压漂移的规律和现有理论基础,文中提出了对应的栅极驱动电路,通过三电平驱动波形的方式来抑制碳化硅MOSFET的阈值电压漂移,并验证了该方案的实际效果。

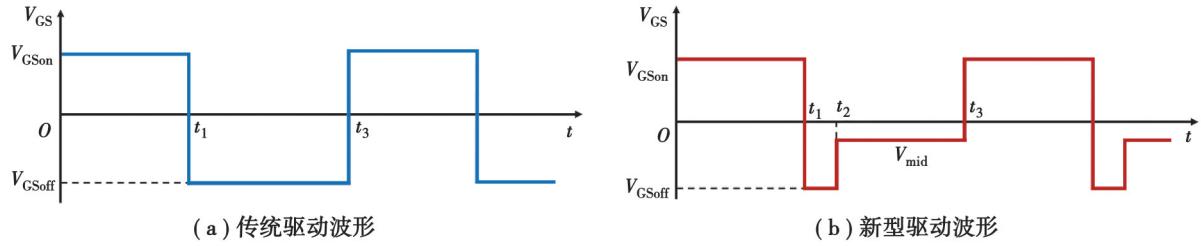

## 1 栅极驱动电路和驱动波形

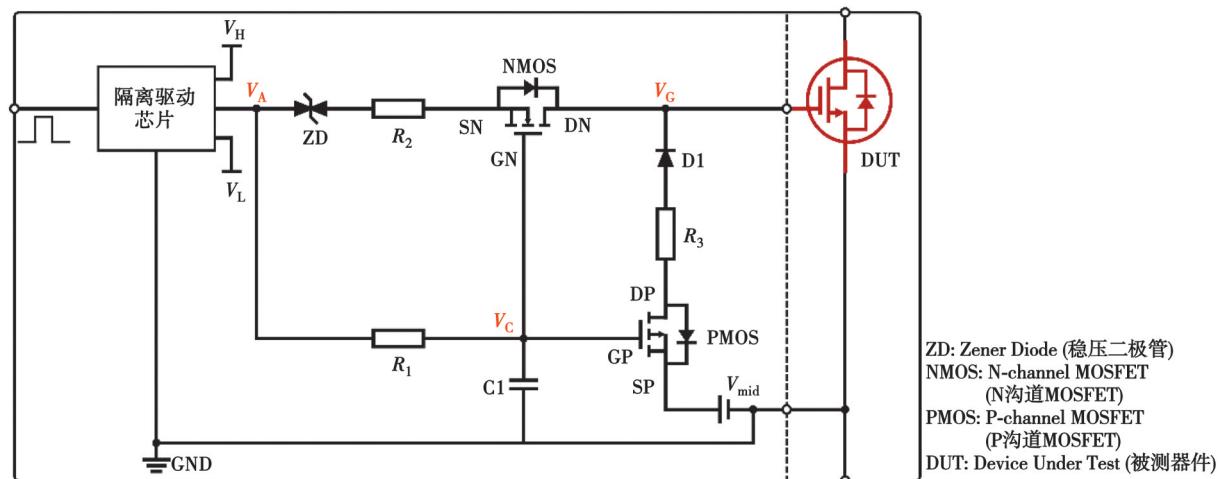

栅极驱动电路包含一个隔离驱动芯片和外围电路,如图1所示,其在被驱动器件栅极上产生的驱动电压波形如图2(b)所示。驱动电压波形包含开通电平 $V_{GSon}$ 、关断电平 $V_{GSoft}$ 和中间电平 $V_{mid}$ 共计3个电平。当被驱动碳化硅MOSFET从开通状态转化为关断状态时,需要一个绝对值较大的负栅极电压来提升关断速度,并且该负压需要持续一段时间直到器件进入关断稳态,因为如串扰等动态扰动一般是发生在桥臂器件切换开关状态的动态过程中的<sup>[14]</sup>。当器件进入关断稳态后,将栅极电压从关断电平切换为中间电平,中间电平的值一般取零电压附近,这样做不仅可以缩短器件开通过程所需要的时间,还可以抑制碳化硅MOSFET的阈值漂移。

图1 栅极驱动电路

Fig. 1 Gate driver circuit

图 2 驱动电压波形

Fig. 2 Driving voltage waveform

可以从 2 个角度来解释该驱动波形抑制碳化硅 MOSFET 抑制阈值漂移的原理：

- 1) 中间电平的存在将器件栅极电压上升过程转化为了 2 次近似为单极性的电压切换过程, 而碳化硅 MOSFET 本身具有单极性栅极电压应力切换几乎不会导致阈值漂移的特点<sup>[12]</sup>。

- 2) 根据局部电场模型<sup>[15]</sup>, 当栅极为关断电压时, 栅极氧化层将捕获大量空穴并形成较强的局部电场, 而切换为中间电压后, 一部分被捕获的空穴将被释放导致局部电场减弱。当器件切换为开通状态的过程中, 较弱的局部电场导致的阈值电压漂移量相对于较强的局部电场导致的阈值电压漂移量更低。

## 2 栅极驱动电路的工作原理

栅极驱动电路的 3 个电平通路如图 3 所示, 其中 ZD(zener diode) 为双向稳压二极管, 用于给 NMOS 管 (N-channel MOSFET, GN) 和源极 (source-NMOS, SN) 之间的电位差, 使其能够正常开启或关断; R2 为高电平通路和低电平通路的驱动电阻; NMOS 管用于连通或阻断低电平通路, 注意高电平通路由于 NMOS 管的反并联二极管而无法阻断; 二极管 D1 用于防止  $V_g$  高于中间电平  $V_{mid}$  时的直接连通; R3 为中间电平通路的驱动电阻; PMOS 管即 p-channel MOSFET、栅极 (gate-PMOS, GP)、漏极 (drain-PMOS, DP) 和源极 (source-PMOS, SP), 用于连通或阻断中间电平通路;  $V_{mid}$  为直流电源, 用于提供需要的中间电平; 电阻 R1 和电容 C1 构成一阶延时电路, 用于控制 NMOS 管和 PMOS 管的开通和关断时间; DUT(device under test) 为被驱动器件。

图 3 各电平通路

Fig. 3 Various voltage paths

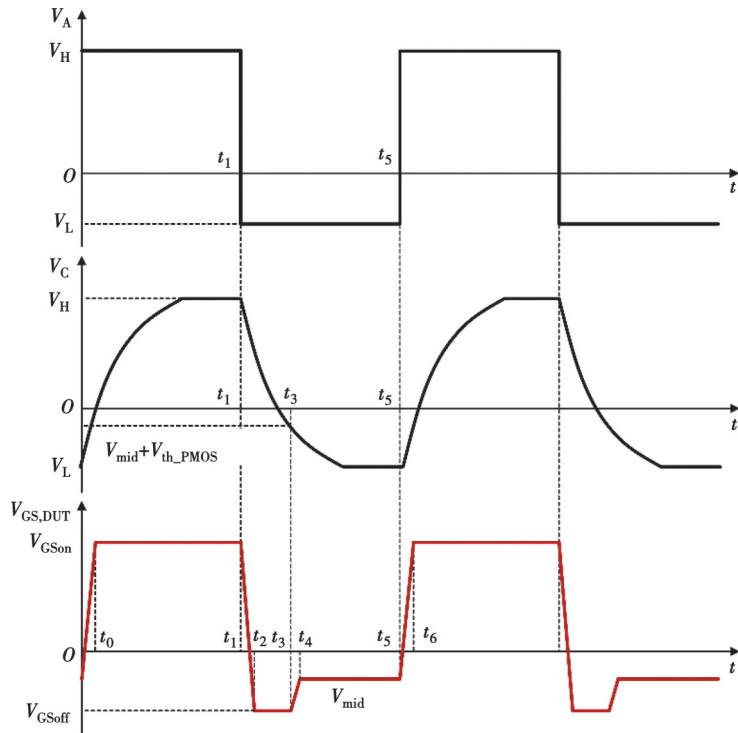

当给隔离驱动芯片施加方波信号时,即可在被驱动器件栅极产生三电平驱动电压波形,其具体工作时序如图4所示。其中,  $V_A$  代表隔离驱动芯片输出电位;  $V_C$  代表电容 C1 两端的电压,也是 NMOS 管和 PMOS 管的栅极电位;  $V_{GS,DUT}$  为被驱动器件的栅极电压,和图3中  $V_g$  的值相对应。高电平  $V_H$ 、中间电平  $V_{mid}$  和低电平  $V_L$  的大小关系为:  $V_L < V_{mid} < V_H$ 。

图4 驱动电路工作时序

Fig. 4 Timing of the driver circuit operation

1) 在  $t_1$  时刻之前, 电路达到稳态, 隔离驱动芯片输出电平  $V_A = V_H$ , 电容 C1 的电压  $V_C = V_A = V_H$ 。此时 NMOS 管栅极电位为  $V_H$ , 源极电压为  $V_H - V_{ZD}$ , 处于开启状态。PMOS 管栅极电位为  $V_H$ , 源极电位为  $V_{mid}$ , 处于关断状态。被驱动器件 DUT 栅极为开通电平  $V_{GSon} = V_H - V_{ZD}$ 。其中  $V_{ZD}$  为双向稳压二极管 ZD 的稳压值, 此时驱动电路与图3(b)所示状态相对应。

2) 在  $t_1$  时刻, 驱动芯片输出由高电平转化为低电平  $V_A = V_L$ , 此时电容 C1 准备开始放电。但 NMOS 管栅极电位依然为  $V_H$ , 源极电位为  $V_L + V_{ZD}$ , 处于导通状态。PMOS 管栅极电位为  $V_H$ , 源极电位为  $V_{mid}$ , 依然为关断状态。隔离驱动芯片输出端与被驱动器件 DUT 的栅极通过 NMOS 管相连, 此时被驱动器件栅极开始转化为关断电平  $V_{Gsoff} = V_L + V_{ZD}$ , 转化速度可以调节 R2 来改变(对应  $t_1$  到  $t_2$  的转化时间)。此时驱动电路与图3(c)所示状态相对应。

3) 在  $t_3$  时刻, 隔离驱动芯片输出依然为低电平  $V_A = V_L$ , 此时电容 C1 放电到 PMOS 管足以开启, 被驱动器件 DUT 栅极被钳位至中间电平  $V_{mid}$ , 随后 NMOS 管关断。被驱动器件 DUT 栅极从关断电平  $V_{Gsoff}$  到中间电平  $V_{mid}$  的转换速度可以调节 R3 来改变(对应  $t_3$  到  $t_4$  的转化时间)。 $t_4$  时刻稳定后 NMOS 管栅极电位为  $V_L$ , 源极电位为  $V_L + V_{ZD}$ , 处于关断状态; PMOS 管栅极电位为  $V_L$ , 源极电位为  $V_{mid}$ , 处于开启状态。此时驱动电路与图3(d)所示状态相对应。

4) 在  $t_5$  时刻, 隔离驱动芯片输出从低电平转换为高电平  $V_A = V_H$ , 此时驱动芯片输出端与被驱动器件 DUT 的栅极通过 NMOS 管的反并联二极管相连, 被驱动器件 DUT 栅极再次回到开通电平  $V_{GSon} = V_H - V_{ZD}$ 。而中间电平通路的二极管 D1 为反向耐压状态。被驱动器件 DUT 栅极从中间电平  $V_{mid}$  到开通电平  $V_{GSon}$  的转换速度可以调节 R2 来改变(对应  $t_5$  到  $t_6$  的转化时间)。电容 C1 充电一段时间后 NMOS 管开启, PMOS 管关断, 驱动电路回到图3(b)对应状态。

电路关断电平  $V_{G\text{off}}$  的持续时间可以调节电阻 R1 和电容 C1 的值来改变。若把 PMOS 管的阈值电压记为  $V_{\text{th\_PMOS}}$ , 电容 C1 在  $t_1$  时刻的电压值记为  $V_{\text{C1}}$ , 则关断电平  $V_{G\text{off}}$  的持续时间  $t_{\text{off}} = t_3 - t_2$  可以由以下式子确定:

$$\begin{cases} V_{\text{th\_PMOS}} = V_{\text{C1}} - V_{\text{mid}}, \\ V_{\text{C1}} = V_{\text{L}} + (V_{\text{H}} - V_{\text{L}}) e^{-(t_3 - t_1)/R_1 C_1}, \\ t_{\text{off}} = t_3 - t_2 = (t_3 - t_1) - (t_2 - t_1), \end{cases} \quad (1)$$

$$t_{\text{off}} = R_1 C_1 \ln \left( \frac{V_{\text{H}} - V_{\text{L}}}{V_{\text{th\_PMOS}} + V_{\text{mid}} - V_{\text{L}}} \right) - (t_2 - t_1)。 \quad (2)$$

其中, 棚极电压下降时间  $(t_2 - t_1)$  可以改变 R2 的值来调节。

### 3 实验验证

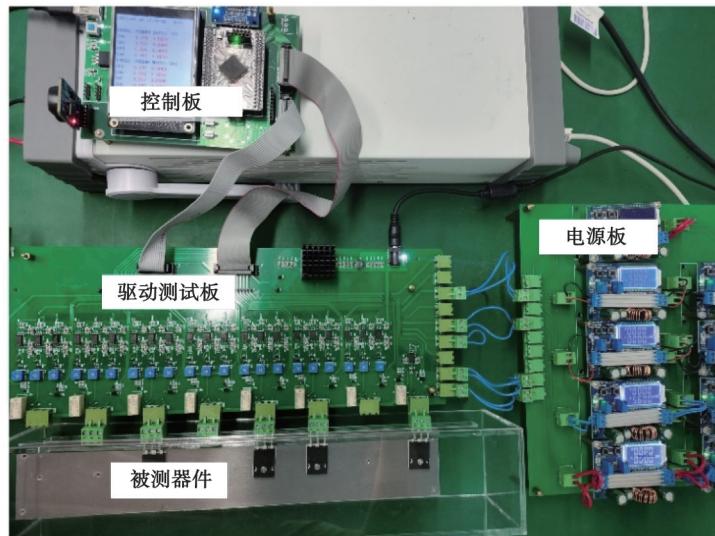

为了验证上述驱动电路对碳化硅 MOSFET 阈值电压漂移的抑制效果, 搭建了如图 5 所示的实验平台。实验平台由控制板、驱动测试板、电源板和被测器件 4 大部分组成。其中, 控制板用于产生 PWM 波和阈值测量时序控制等功能; 驱动测试板即为第 2 节所介绍的棚极驱动电路; 电源板用于提供开通电平、关断电平和各个等级的中间电平; 被测器件型号为 SCT3120AL, 是 Rohm 生产的一款商用碳化硅 MOSFET 器件。实验关键参数设置和关键元件的取值如表 1 所示。

图 5 实验平台

Fig. 5 Experimental platform

表 1 实验参数设置

Table 1 Experimental parameter settings

| 参数名称                        | 取值    | 参数名称                           | 取值  |

|-----------------------------|-------|--------------------------------|-----|

| 开关频率 $f_s/\text{kHz}$       | 150   | 稳压管电压 $V_{\text{ZD}}/\text{V}$ | 2.4 |

| 占空比 $D$                     | 0.5   | 电阻 $R_2/\Omega$                | 27  |

| 高电平 $V_{\text{H}}/\text{V}$ | 17.4  | 电阻 $R_1/\Omega$                | 20  |

| 低电平 $V_{\text{L}}/\text{V}$ | -12.4 | 电容 $C_1/\text{nF}$             | 10  |

| 实验温度 $T/\text{°C}$          | 25    | $V_{\text{th\_PMOS}}/\text{V}$ | -2  |

结合表 1 和第 2 节的电路分析, 可以确定被驱动器件的开通电平和关断电平分别为

$$\begin{cases} V_{\text{Gson}} = V_{\text{H}} - V_{\text{ZD}} = 15 \text{ V}, \\ V_{\text{Gsoff}} = V_{\text{L}} + V_{\text{ZD}} = -10 \text{ V}。 \end{cases} \quad (3)$$

当中间电平取0 V时,由式(2)可得栅极电压下降时间与关断电平持续时间之和为

$$t_3 - t_1 = R_1 C_1 \ln \left( \frac{V_H - V_L}{V_{th\_PMOS} + V_{mid} - V_L} \right) = 210 \text{ ns}。 \quad (4)$$

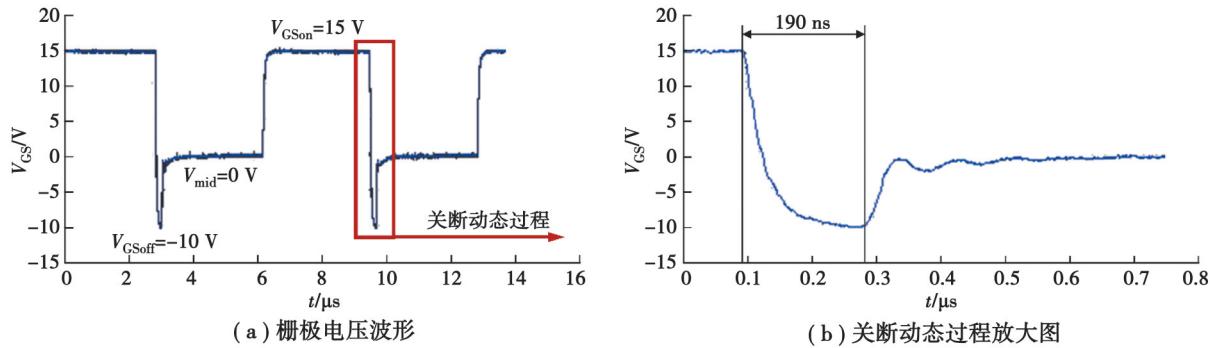

该分析结果与实验平台产生的实际波形(见图6)所对应,实际波形的 $t_3 - t_1$ 约为190 ns,与理论计算的误差在可接受范围内。

图6  $V_{mid}=0$  V时对应的栅极电压波形

Fig. 6 Gate voltage waveform corresponding to  $V_{mid}=0$  V

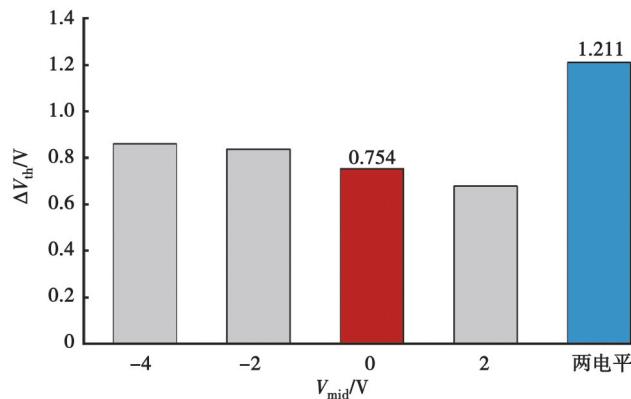

图7展示了进行70 h的老化实验后被测器件阈值电压漂移量 $\Delta V_{th}$ 随不同中间电平值 $V_{mid}$ 的变化关系,其中横坐标最右侧的“两电平”代表对照组的实验结果,即只包含开通电平 $V_{GSon}$ 和关断电平 $V_{GSoff}$ ,也可以认为中间电平 $V_{mid} = V_{GSoff}$ 。实验测试了中间电平为0 V附近的情况,使得中间电平持续时间内器件保持关断状态。因为高于0 V的中间电平可能会使器件进入一个漏电流非常大的非完全关断状态或者进入一个导通电阻非常大的导通状态。上述2种非正常状态都将导致器件的损耗增大,这是实际应用中应该避免的情况。

图7 实验结果

Fig. 7 Experimental results

根据局部电场理论,中间电平越高,越能帮助关断电平期间被捕获的正电荷的释放,局部电场减弱得越快,从中间电平切换为开通电平过程导致的阈值漂移就会越低。故被测器件的阈值电压漂移量随中间电平的增加呈现逐步降低的趋势。

由图7可知,在如前所述的实验条件下,对被测器件施加70 h的栅极电压应力后,文中所述的三电平驱动方式导致的阈值电压漂移量明显低于传统两电平驱动方式导致的阈值电压漂移量。当中间电平 $V_{mid}$ 取0 V时,相对于两电平驱动方式的阈值电压漂移量降低了37%。

## 4 结束语

1)提出的驱动电路通过在驱动电压波形中引入中间电平的方式,减弱了“局部电场效应”,进而达到抑制碳化硅 MOSFET 阈值电压漂移的目的。

2)该驱动方法对解决碳化硅 MOSFET 阈值电压漂移问题提供了新的思路,在实际应用中对于提高碳化硅 MOSFET 可靠性具备一定参考价值。

3)该驱动电路虽然对碳化硅 MOSFET 阈值电压漂移有一定抑制效果,但不能完全消除器件的阈值电压漂移现象,由于驱动电路较为复杂并且驱动电路本身的功耗也有所增加,所以该驱动电路在应用中带来的收益与损害还需要根据实际情况作进一步分析。

## 参考文献

- [1] Zhang Q J, Wang G Y, Doan H, et al. Latest results on 1200 V<sub>th</sub> H-SiC CIMOSFETs with  $r_{sp}$  on of 3.9 mΩ·cm<sup>2</sup> at 150°C[C]// 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC's (ISPSD). May 10-14, 2015, Hong Kong, China. IEEE, 2015: 89-92.

- [2] 白志强. 4H-SiC 功率 MOSFETs 的可靠性研究[D]. 西安: 西安电子科技大学, 2022.

Bai Z Q. Research on reliability of 4H-SiC power MOSFETs[D]. Xi'an: Xidian University, 2022. (in Chinese)

- [3] 江希. 碳化硅 MOSFET 坚固性与可靠性研究[D]. 长沙: 湖南大学, 2021.

Jiang X. Research on ruggedness and reliability of silicon carbide MOSFET[D]. Changsha: Hunan University, 2021. (in Chinese)

- [4] Hazra S, Madhusoodhanan S, Moghaddam G K, et al. Design considerations and performance evaluation of 1200-V 100-a SiC MOSFET-based two-level voltage source converter[J]. IEEE Transactions on Industry Applications, 2016, 52(5): 4257-4268.

- [5] Hazra S, De A K, Cheng L, et al. High switching performance of 1700-V, 50-a SiC power MOSFET over Si IGBT/BiMOSFET for advanced power conversion applications[J]. IEEE Transactions on Power Electronics, 2016, 31(7): 4742-4754.

- [6] Zhao B, Song Q, Liu W H. A practical solution of high-frequency-link bidirectional solid-state transformer based on advanced components in hybrid microgrid[J]. IEEE Transactions on Industrial Electronics, 2015, 62(7): 4587-4597.

- [7] Aichinger T, Rescher G, Pobegen G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs[J]. Microelectronics Reliability, 2018, 80: 68-78.

- [8] Asllani B, Castellazzi A, Salvado O A, et al.  $V_{th}$ -hysteresis and interface states characterisation in SiC power MOSFETs with planar and trench gate[C]//2019 IEEE International Reliability Physics Symposium (IRPS). March 31-April 4, 2019. Monterey, CA, USA. IEEE, 2019: 1-6.

- [9] Ang D S, Wang S, Du G A, et al. A consistent deep-level hole trapping model for negative bias temperature instability[J]. IEEE Transactions on Device and Materials Reliability, 2008, 8(1): 22-34.

- [10] Zhou W C, Zhong X Q, Sheng K. High temperature stability and the performance degradation of SiC MOSFETs[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2329-2337.

- [11] Jiang H P, Zhong X H, Qiu G Q, et al. Dynamic gate stress induced threshold voltage drift of silicon carbide MOSFET[J]. IEEE Electron Device Letters, 2020, 41(9): 1284-1287.

- [12] Zhong X H, Jiang H P, Qiu G Q, et al. Bias temperature instability of silicon carbide power MOSFET under AC gate stresses [J]. IEEE Transactions on Power Electronics, 2022, 37(2): 1998-2008.

- [13] Zhang Z Y, Wang F, Tolbert L M, et al. Active gate driver for fast switching and cross-talk suppression of SiC devices in a phase-leg configuration[C]//2015 IEEE Applied Power Electronics Conference and Exposition (APEC). March 15-19, 2015, Charlotte, NC, USA. IEEE, 2015: 774-781.

- [14] Liu C H, Zhang Z D, Liu Y F, et al. Smart self-driving multilevel gate driver for fast switching and crosstalk suppression of SiC MOSFETs[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 442-453.

- [15] Jiang H P, Qi X W, Qiu G Q, et al. A physical explanation of threshold voltage drift of SiC MOSFET induced by gate switching [J]. IEEE Transactions on Power Electronics, 2022, 37(8): 8830-8834.

(编辑 詹燕平)