doi: 10.11835/j.issn.1000-582X.2025.210

引用格式:赵留青,梁钰茜,牛富丽,等.混合 SiC/Si 有源钳位三电平光储功率模块电热优化设计[J].重庆大学学报,2025,48(11): 25-40.

# 混合 SiC/Si 有源钳位三电平光储功率模块 电热优化设计

赵留青, 梁钰茜, 牛富丽, 邹铭锐, 曾正

(重庆大学 输变电装备技术全国重点实验室, 重庆 400044)

**摘要:**得益于高效率优势,混合 SiC/Si 有源钳位(active neutral point clamped, ANPC)三电平电路拓扑在光储发电系统中应用广泛。但传统混合 SiC/Si 功率模块中, Si 器件的使用限制了效率提升, SiC 器件引入后又可能导致热分布不均、电压过冲及振荡等问题。提出了一种综合设计方法, 结合功率器件损耗均衡与功率模块布局寄生电感优化, 以提高混合 SiC/Si ANPC 电路拓扑的功率模块性能。建立了功率模块损耗模型, 并进行热性能优化, 降低结温与芯片温差; 构建了寄生电感模型, 通过优化设计减小寄生电感; 研制了基于 ANPC 拓扑的混合 SiC/Si 功率模块, 并开展电热性能测试。实验结果验证了功率模块在损耗、寄生电感及热分布方面的显著优势。

**关键词:**三电平拓扑;有源钳位;混合 SiC/Si 功率模块;电-热优化设计

中图分类号:TM464

文献标志码:A

文章编号:1000-582X(2025)11-025-16

## Electro-thermal optimization design of a hybrid SiC/Si power module with active clamped three-level topology for photovoltaic and energy storage applications

ZHAO Liuqing, LIANG Yuxi, NIU Fuli, ZOU Mingrui, ZENG Zheng

(State Key Laboratory of Power Transmission Equipment Technology, Chongqing University,

Chongqing 400044, P. R. China)

**Abstract:** The active neutral point clamped (ANPC) three-level topology with hybrid SiC and Si power module is widely used in photovoltaic and energy storage systems due to its high efficiency. However, in conventional hybrid SiC/Si power modules, the use of Si devices constrains efficiency improvements, while the introduction of SiC devices can lead to challenges such as uneven heat distribution, voltage overshoot, and oscillation. To address

收稿日期:2024-12-25 网络出版日期:2025-03-27

基金项目:国家自然科学基金资助项目(52177169);重庆市杰出青年科学基金资助项目(CSTB2024NSCQ-JQX0016);重庆市研究生科研创新训练资助项目(CYB240023)。

Supported by the National Natural Science Foundation of China (52177169), Natural Science Foundation of Chongqing (CSTB2024NSCQ-JQX0016), and the Projects of Chongqing Postgraduate Scientific Research and Innovation Training Program (CYB240023).

作者简介:赵留青(2000—),女,硕士研究生,主要从事新型电力电子器件封装集成与应用研究,(E-mail) zlqliuqing@163.com。

通信作者:牛富丽,女,讲师,(E-mail) niufuli@cqu.edu.cn。

these issues, this paper proposes a comprehensive design method that incorporates both loss equalization of power devices and parasitic inductance optimization of the module layout to improve the performance of hybrid SiC/Si ANPC modules. First, a loss model of the power module is established, and thermal performance is optimized to reduce junction temperatures and chip-to-chip temperature differences. Second, a parasitic inductance model is constructed, and inductance is minimized through optimized layout design. Finally, a hybrid SiC/Si power module based on the ANPC topology is developed and experimentally evaluated. The results demonstrate significant improvements in terms of power loss, parasitic inductance, and thermal distribution, verifying the effectiveness of the proposed electro-thermal optimization design.

**Keywords:** three-level topology; active neutral-point clamped; hybrid SiC/Si power module; electro-thermal optimization design

高效率、高功率密度和低成本是光储变流器的核心追求目标<sup>[1]</sup>。三电平 ANPC (active neutral point clamped) 拓扑因其较低的开关损耗和成本优势, 在光储系统中得到广泛应用。随着全 Si 型拓扑性能接近理论极限, 混合碳化硅(SiC)型拓扑因此在光伏发电等领域得到广泛应用<sup>[2-3]</sup>。尽管 SiC 器件能够有效减小开关损耗并提高系统效率, 但其引发的热管理、电磁兼容性等问题仍然存在<sup>[4]</sup>。因此, 基于 ANPC 拓扑的混合 SiC/Si 功率模块热分布和寄生电感优化问题, 成为当前研究热点。

在热分布方面, 损耗不均衡、电流密度分布不均和散热不均等因素直接影响功率模块的热性能<sup>[5-11]</sup>。在混合 SiC 型功率模块配置中, 不同器件的开关特性和导通特性有所不同, 会造成某些区域的热量积聚, 形成温差。尤其是 Si 和 SiC 材料的热导率差异, 使得现有损耗模型未能完全表征混合 SiC 功率模块的热特性, 导致混合 SiC 功率模块热特性的定量评估仍不充分。热分布不均衡会导致局部过热, 影响器件寿命及系统稳定性, 因此, 优化热分布成为关键<sup>[12-17]</sup>。在寄生电感方面, 引入 SiC 功率器件虽可提升开关性能, 但回路中的寄生电感仍对系统稳定性产生影响, 容易引发过电压和电压振荡<sup>[18-19]</sup>。为了减少寄生电感和电磁干扰 (electromagnetic interference, EMI) 噪声, 提出了 P-Cell/N-Cell 概念和混合封装结构, 以降低回路寄生电感<sup>[20-22]</sup>。然而, 由于三电平拓扑涉及多个回路, 现有的设计方法缺乏系统且有效的理论指导, 对于混合 SiC ANPC 功率模块的寄生电感建模与优化仍然需要简单有效的方法<sup>[23-24]</sup>。

首先建立了混合 SiC/Si 功率模块的损耗模型, 并刻画了混合功率模块的寄生电感模型。通过有限元仿真软件和多物理场分析方法, 研究了混合功率模块拓扑选型对热性能的影响。然后, 基于换流回路原理, 提出了混合功率模块的寄生电感优化设计方法, 并通过仿真验证了其有效性。最后, 研制了基于 ANPC 拓扑的混合 SiC/Si 功率模块样机, 并搭建了面对面变流器对拖实验平台。通过不同工况下的光储逆变器电热性能实验, 验证了所提模块在降低芯片结温、均衡结温分布和延长光储变流器寿命方面的有效性。

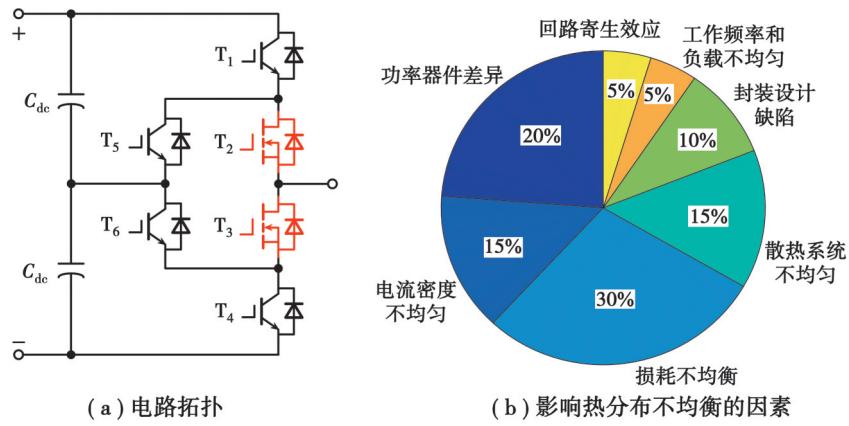

## 1 混合 SiC/Si ANPC 功率模块的电热模型

图 1 为典型的混合 SiC/Si ANPC 电路拓扑及其热分布特性图。由图 1(a)可知, 该拓扑采用 1/3 混合 SiC MOSFET 电路, 以降低模块成本。其中,  $T_1, T_4, T_5, T_6$  由 Si IGBT 和 Si FRD 组成,  $T_2$  和  $T_3$  为具有体二极管的 SiC MOSFET。Si IGBT 工作在工频开关模式, SiC MOSFET 工作在高频开关模式。直流母排电容  $C_{dc}$  为薄膜电容, 起滤波、共模电压抑制、支撑中点电位稳定等。由图 1(b)可见, 不同类型功率器件的特性差异, 是导致其电-热分布不均衡的主要因素。对于文中设计的混合 SiC/Si 功率模块, 不同类型的功率器件导致损耗不均衡。为了分析由于损耗不均匀引起的热分布不均匀问题, 需要建立混合功率模块损耗模型。同时, 由于 SiC MOSFET 被引入复杂长换流回路中, 会引起电压振荡和过冲等问题, 因此需要构建混合功率模块的寄生电感模型。

图 1 混合 SiC/Si ANPC 电路拓扑及热分布问题

Fig. 1 Topology and thermal distribution issues of hybrid SiC/Si ANPC power module

## 1.1 混合 SiC/Si ANPC 功率模块的功率损耗模型

### 1.1.1 Si IGBT 和 Si FRD 的损耗模型

在一个开关周期中, 功率器件导通损耗主要决定于占空比和负载电流。文中采用 SPWM 调制法, 低功耗的 SiC 器件承担全部的高频开关动作, Si 器件工作于工频开关频率。由于每相桥臂的上下半桥对称性, 文中仅分析上半桥臂功率器件的损耗。在一个正弦周期内, Si IGBT 和 Si FRD 的导通损耗, 以  $T_1, D_1$  为例,  $P_{T1cd}$  与  $P_{D1cd}$  可表示为

$$\begin{cases} P_{T1cd} = \frac{1}{2\pi} \int_{\alpha}^{\beta} d_T (V_{CE0} + r_{CE} i_p) i_p d\theta = \frac{1}{2\pi} \int_{\varphi}^{\pi} d_T [V_{CE0} + r_{CE} I_m \sin(\theta - \varphi)] I_m \sin(\theta - \varphi) d\theta = V_{CE0} I_{Tavg} + r_{CE} I_{Trms}^2, \\ P_{D1cd} = \frac{1}{2\pi} \int_{\alpha}^{\beta} d_D (V_{F0} + r_F i_p) i_p d\theta = -\frac{1}{2\pi} \int_{0}^{\varphi} d_D [V_{F0} - r_F I_m \sin(\theta - \varphi)] I_m \sin(\theta - \varphi) d\theta = V_{F0} I_{Davg} + r_F I_{Drms}^2. \end{cases} \quad (1)$$

式中:  $i_p$  为变流器的输出相电流;  $d_T, d_D$  分别为 IGBT 和二极管的占空比;  $V_{CE0}, V_{F0}$  分别为 IGBT 的饱和压降和 FRD 的门槛电压;  $r_{CE}, r_F$  分别为 IGBT 和二极管的导通电阻;  $I_{Tavg}, I_{Trms}$  分别为流经 IGBT 电流的平均值和有效值;  $I_{Davg}, I_{Drms}$  分别为流经二极管电流的平均值和有效值;  $\varphi$  为负载功率因数角。

对于开关损耗, 在一个正弦周期内, Si IGBT 和 Si FRD 的平均开关损耗, 以  $T_1, D_1$  为例,  $P_{T1sw}$  与  $P_{D1sw}$  可表示为

$$\begin{cases} P_{T1sw} = \frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{\alpha}^{\beta} \sin(\theta - \varphi) d\theta = \frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{\varphi}^{\pi} \sin(\theta - \varphi) d\theta = \frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} (1 + \cos \varphi), \\ P_{D1sw} = \frac{E_{rec} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{\alpha}^{\beta} \sin(\theta - \varphi) d\theta = -\frac{E_{rec} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{0}^{\varphi} \sin(\theta - \varphi) d\theta = \frac{E_{rec} V_{dc} f_s I_m}{2\pi V_n I_n} (1 - \cos \varphi). \end{cases} \quad (2)$$

式中: 开关损耗  $E_{sw}$  为开通损耗  $E_{on}$  和关断损耗  $E_{off}$  之和,  $E_{sw} = E_{on} + E_{off}$ ;  $f_s$  为开关频率;  $V_{dc}$  为直流母线电压;  $V_n$  和  $I_n$  分别为开关损耗测试条件下的  $V_{ce}$  和  $I_c$ ;  $E_{rec}$  为二极管反向恢复损耗。

同理, ANPC 三电平变换器上桥臂其他功率器件的导通损耗和开关损耗, 可以表示为

$$\begin{cases} P_{T5cd} = \frac{1}{2\pi} \int_{\alpha}^{\beta} d_T (V_{CE0} + r_{CE} i_p) i_p d\theta = \frac{1}{2\pi} \int_{\pi+\varphi}^{2\pi} [V_{CE0} + r_{CE} I_m \sin(\theta - \varphi)] I_m \sin(\theta - \varphi) d\theta = V_{CE0} I_{Tavg} + r_{CE} I_{Trms}^2, \\ P_{D5cd} = \frac{1}{2\pi} \int_{\alpha}^{\beta} d_D (V_{F0} + r_F i_p) i_p d\theta = -\frac{1}{2\pi} \int_{\pi}^{\pi+\varphi} (1 - |d_D|) [V_{F0} - r_F I_m \sin(\theta - \varphi)] I_m \sin(\theta - \varphi) d\theta = V_{F0} I_{Davg} + r_F I_{Drms}^2; \end{cases} \quad (3)$$

$$\begin{cases} P_{T5sw} = \frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{\alpha}^{\beta} \sin(\theta - \varphi) d\theta = \frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{\pi+\varphi}^{2\pi} \sin(\theta - \varphi) d\theta = -\frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} (1 + \cos \varphi), \\ P_{D5sw} = \frac{E_{rec} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{\alpha}^{\beta} \sin(\theta - \varphi) d\theta = -\frac{E_{rec} V_{dc} f_s I_m}{2\pi V_n I_n} \int_{\pi}^{\pi+\varphi} \sin(\theta - \varphi) d\theta = -\frac{E_{rec} V_{dc} f_s I_m}{2\pi V_n I_n} (1 - \cos \varphi). \end{cases} \quad (4)$$

### 1.1.2 SiC MOSFET 的损耗模型

在一个调制波周期内,  $T_2$  和  $T_3$  交替导通,  $T_2$  和  $T_3$  导通损耗相同。考虑到 SiC MOSFET 在死区时间  $T_d$  内, 负荷电流通过其体二极管续流; 在死区时间之外, 负荷电流通过其沟道续流。因此,  $T_2$  或  $T_3$  通过体二极管续流的时间为  $T_d f_s$ ,  $T_2$  或  $T_3$  通过 MOSFET 沟道续流的时间为  $(1 - T_d f_s)$ , 以  $T_2$  为例, SiC MOSFET 及其体二极管导通损耗  $P_{T2cd}$  与  $P_{D2cd}$  可以表示为

$$\begin{cases} P_{T2cd} = \frac{(1 - T_d f_s)}{2\pi} \left[ \int_0^\pi d_T r_{DS} i_p^2 d\theta + \int_\pi^{2\pi} (1 - d_T) r_{DS} i_p^2 d\theta \right] = r_{DS} I_{Trms}^2, \\ P_{D2cd} = \frac{T_d f_s}{4\pi} \int_0^{2\pi} d_D V_{FO} i_p d\theta = V_{FO} I_{Davg} \end{cases} \quad (5)$$

式中,  $r_{DS}$  为 SiC MOSFET 的沟道导通电阻。

对于开关损耗, 在一个正弦周期内, SiC MOSFET 的平均开关损耗  $P_{T2sw}$  可以表示为

$$P_{T2sw} = \frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} \int_a^\beta \sin(\theta - \varphi) d\theta = 2 \frac{E_{sw} V_{dc} f_s I_m}{2\pi V_n I_n} \int_0^\pi \sin(\theta - \varphi) d\theta = \frac{2E_{sw} V_{dc} f_s I_m}{\pi V_n I_n} \cos \varphi, \quad (6)$$

式中,  $E_{sw}$  为 SiC MOSFET 的开关损耗。

由于体二极管仅在死区内导通, 在换流的过程中,  $T_2$  或  $T_3$  电压一直被钳位为零,  $T_2$  或  $T_3$  体二极管的反向恢复损耗可以忽略不计。

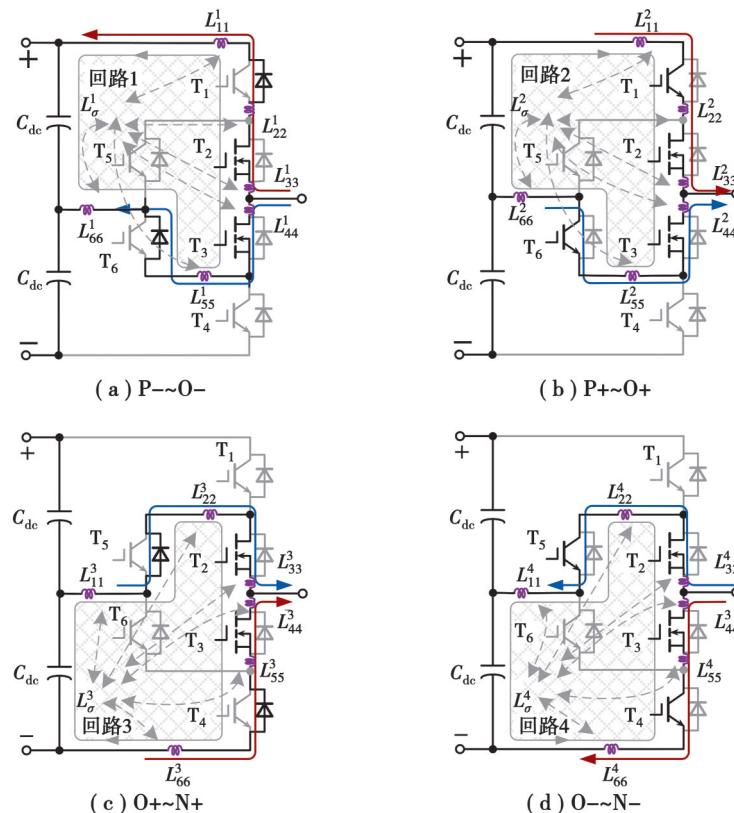

### 1.2 混合 SiC/Si ANPC 功率模块的寄生电感模型

为了实现混合功率模块低寄生电感优化设计, 文中建立光储用混合功率模块的寄生电感的数学模型, 观察式(7)。基于三电平换流回路原理, 分析功率模块内寄生电感的影响, 以芯片为分割界限, 将每个换流回路分成 6 段导体。因此, 考虑每段导体的自感, 以及导体之间的互感, 构建混合 SiC/Si ANPC 功率模块寄生电感模型, 如图 2 所示。

图 2 混合 SiC/Si ANPC 功率模块寄生电感模型

Fig. 2 Parasitic inductance model of hybrid SiC/Si ANPC power module

在图 2 中,  $\mathbf{L}_\sigma^i$  ( $i=1, 2, 3, 4$ ) 为功率模块回路寄生电感矩阵,  $\mathbf{L}_\sigma^1$  代表 P-~O-~回路寄生电感;  $\mathbf{L}_\sigma^2$  代表 P+~O+~回路寄生电感;  $\mathbf{L}_\sigma^3$  代表 O+~N+~回路寄生电感;  $\mathbf{L}_\sigma^4$  代表 O-~N-~回路寄生电感。每条回路寄生电感都分别由六段导体的自感  $L_{nn}^i$  ( $i=1, 2, 3, 4, n=1, 2, 3, 4, 5, 6$ ) 和互感  $M_{mm}^i$  ( $i=1, 2, 3, 4, m \neq n, m, n=1, 2, 3, 4, 5, 6$ ) 影响而得, 即

$$\mathbf{L}_\sigma^i = \begin{bmatrix} L_{11}^i & M_{12}^i & \cdots & M_{16}^i \\ M_{21}^i & L_{22}^i & \cdots & M_{26}^i \\ \vdots & \vdots & \ddots & \vdots \\ M_{61}^i & M_{62}^i & \cdots & L_{66}^i \end{bmatrix} \circ \quad (7)$$

## 2 混合 SiC/Si ANPC 功率模块的电热设计

### 2.1 损耗均衡优化

常见的损耗均衡设计方法可通过改变调制方式、信号处理算法优化等软件方法, 提高系统效率; 也可通过改变器件等, 采用高性能低功耗的电子元件等硬件方法, 以降低系统损耗。为了实现混合 SiC/Si ANPC 拓扑的损耗均衡设计, 对比常见的混合 SiC SBD、混合 SiC MOSFET、全 Si 这 3 种电路拓扑。在相同电压电流等级下, 采用 SPWM 调制, 对每个拓扑进行器件选型。同一类型的器件选择对应电压电流等级下的相同型号和数量, 以综合考虑损耗均衡、效率、损耗大小、成本等因素。其参数如表 1 所示。

表 1 ANPC 三电平变流器的关键参数

Table 1 Key parameters of ANPC three-level converter

| 设备                        | 参数                                                                                                                             |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 变流器                       | $V_{dc}=1500$ V, $C_{dc}=900$ $\mu$ F, $f_0=50$ Hz, $V_{ac}=690$ V, $\cos\varphi=\pm 1$ , $f_s=16$ kHz, $P=200$ kW, $L_f=1$ mH |

| Si IGBT(200 A/1 200 V)    | $V_{ce0}=0.82$ V, $r_{ce}=7.5$ m $\Omega$ , $E_{on}=14.3$ mJ, $E_{off}=17.5$ mJ, $V_n=600$ V, $I_n=225$ A                      |

| Si FRD(200 A/1 200 V)     | $V_{fo}=0.93$ V, $r_f=3.1$ m $\Omega$ , $E_{rec}=11.1$ mJ, $V_n=600$ V, $I_n=200$ A                                            |

| SiC SBD(100 A/1 200 V)    | $V_{fo}=0.92$ V, $r_f=4.97$ m $\Omega$ , $E_{rec}=0.68$ mJ, $V_n=500$ V, $I_n=100$ A                                           |

| SiC MOSFET(100 A/1 200 V) | $r_{ds}=8.8$ m $\Omega$ , $E_{on}=3.28$ mJ, $E_{off}=0.32$ mJ, $V_n=400$ V, $I_n=100$ A                                        |

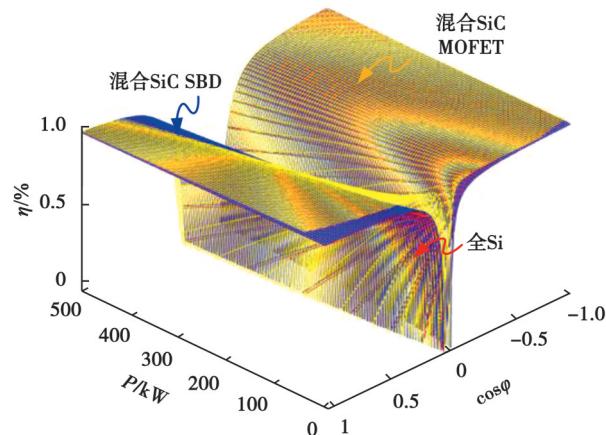

为分析不同拓扑的效率, 设定母线电压  $V_{dc}=1500$  V, 开关频率为 16 kHz。基于 1.1 节建立的损耗模型, 考虑热电耦合, 采用 25 °C 下功率器件数据, 用于评估上述 3 种拓扑在不同输入功率下和不同功率因数下的效率, 如图 3 所示。随着输入功率  $P$  的增大, 3 种拓扑的损耗均有所上升, 导致效率  $\eta$  逐渐降低。特别是混合 SiC MOSFET 拓扑在功率因数小于零时, 其效率始终高于其余 2 种拓扑。在功率因数  $\cos\varphi$  大于 0 且接近 1 时, 效率达到最高水平。而全 Si ANPC 由于 Si IGBT 的开关损耗较高, 表现出相对较低的效率。

图 3 3 种 ANPC 功率模块的效率对比

Fig. 3 Efficiency comparison of three ANPC power modules

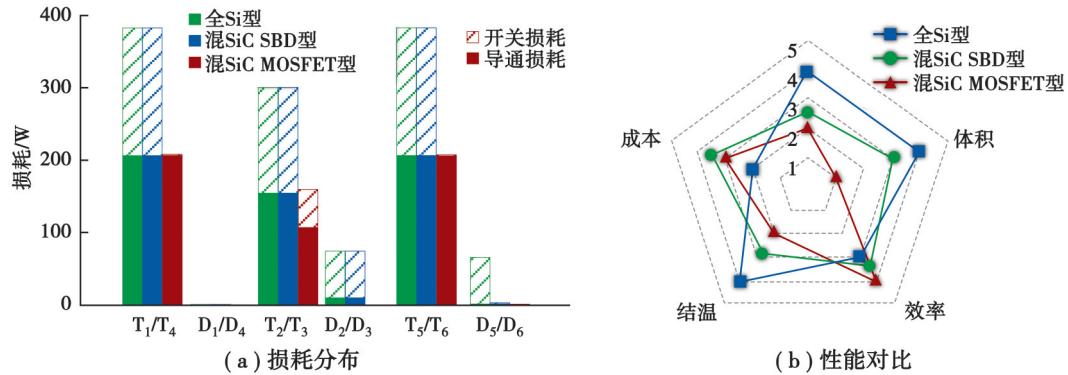

为分析不同拓扑的损耗分布情况,设定  $V_{dc}=1500$  V,开关频率为 10 kHz,输入功率为 200 kW,功率因数为 0.8,并计算 3 种拓扑的损耗,其损耗分布如图 4(a)所示。混合 SiC MOSFET 型拓扑总损耗比混合 SiC SBD 型拓扑低 164.4 W,比全 Si 型拓扑低 220.2 W。综合考虑损耗均衡、效率、损耗大小及成本等因素,从图 4(b)可以直观地得出,混合 SiC MOSFET 型 ANPC 三电平拓扑的损耗更低、更均衡,因而更适合于光储发电系统。

图 4 3 种 ANPC 拓扑的损耗分布及性能对比

Fig. 4 Loss distribution and performance comparison of three ANPC topologies

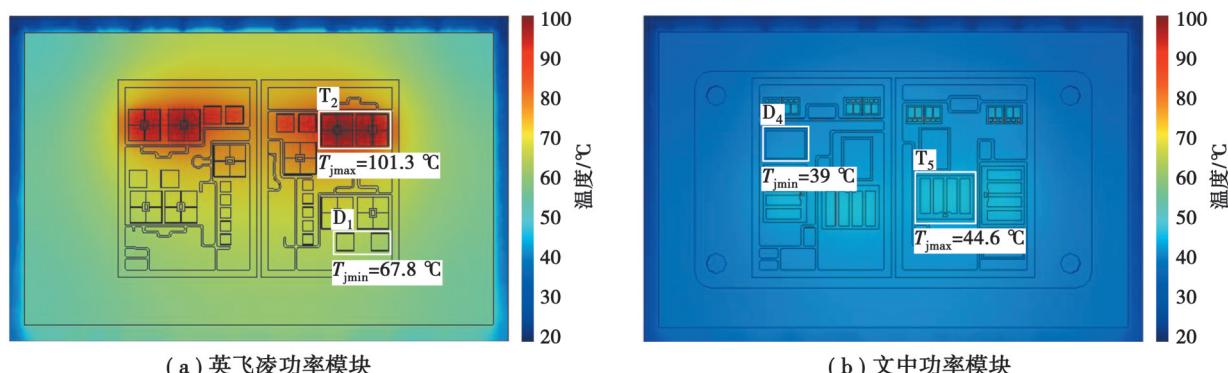

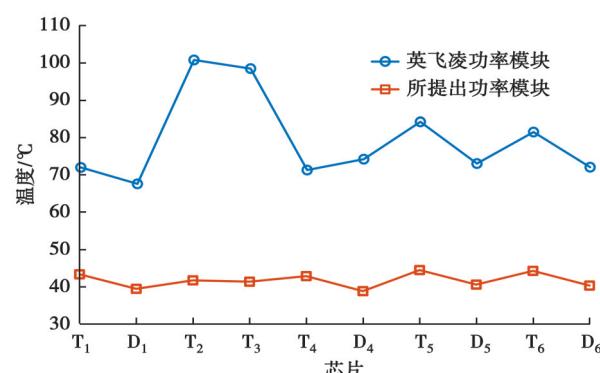

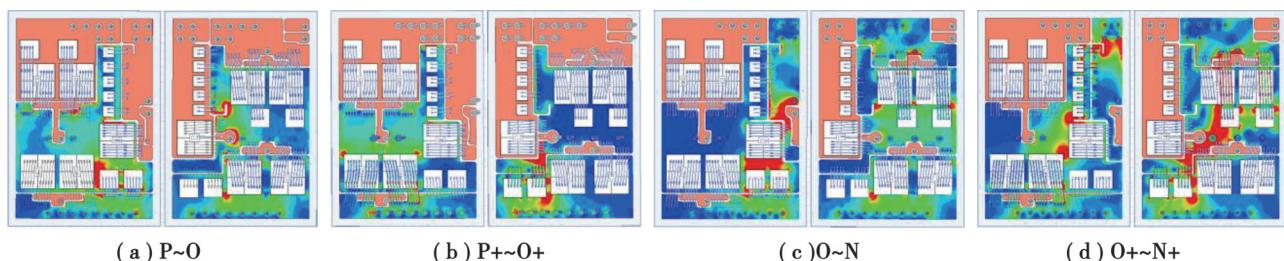

文中采用混合 SiC MOSFET 型 ANPC 拓扑设计功率模块。为了评估文中功率模块在实际工况下的热可靠性,利用 1.1 节的损耗模型,计算出英飞凌模块 F3L400R10W3S7F\_B11 和文中混合 SiC/Si 模块实际工况下的损耗,并将每个芯片的损耗作为 COMSOL 仿真的热源,观察模块的最大结温和热分布情况。图 5 为仿真的英飞凌模块和文中混合模块的热分布图,图 6 为 2 个模块不同芯片结温的对比图。

图 5 文中功率模块与英飞凌功率模块的温度仿真结果

Fig. 5 The temperature simulation results of the proposed power module and the Infineon power module

图 6 文中功率模块与英飞凌功率模块的芯片结温对比

Fig. 6 Comparison of chip junction temperatures between proposed and Infineon power modules

从图 5 和图 6 可以看出, 英飞凌模块温度分布不均匀, 最高结温为  $101.3^{\circ}\text{C}$ , 最大温差为  $33.4^{\circ}\text{C}$ , 其中  $T_2$ 、 $T_3$  位于结温最高处, 处于模块在高温运行时较为薄弱的环节。而文中混合模块将损耗集中在开关损耗极小的 SiC MOSFET 上, 温度分布较为均匀, 最高结温是  $44.6^{\circ}\text{C}$ , 最大温差为  $5.7^{\circ}\text{C}$ , 较英飞凌模块最高结温降低了 56%。文中混合功率模块有效降低损耗, 并实现了更优的损耗均衡。

## 2.2 低寄生电感设计

为了减少引入 SiC MOSFET 所引起的电压过冲问题, 需要进行低寄生电感设计。根据式(7)可知, 减小寄生电感, 可以采取减少导体自感和增强负互感的措施。在降低自感方面, 应在有限的空间内实现较短的换流回路, 以减小每条回路中导体的自感。因此, 通过缩短键合线长度、降低键合线拱高和增加 (direct bonding copper, DBC) 铜厚等方法, 可以有效减少导体自感, 从而降低功率模块封装的寄生电感。在增强负互感方面, 可以采用磁场相消原理, 设计将电流方向相反的 2 个换流回路进行精确布局。当一个回路中的电流流动方向与另一个回路相反时, 产生的磁场在空间上相互作用。通过优化回路的几何布局, 使得两者的磁通量相互重叠并形成相消效应, 从而显著减弱局部区域内的磁场。

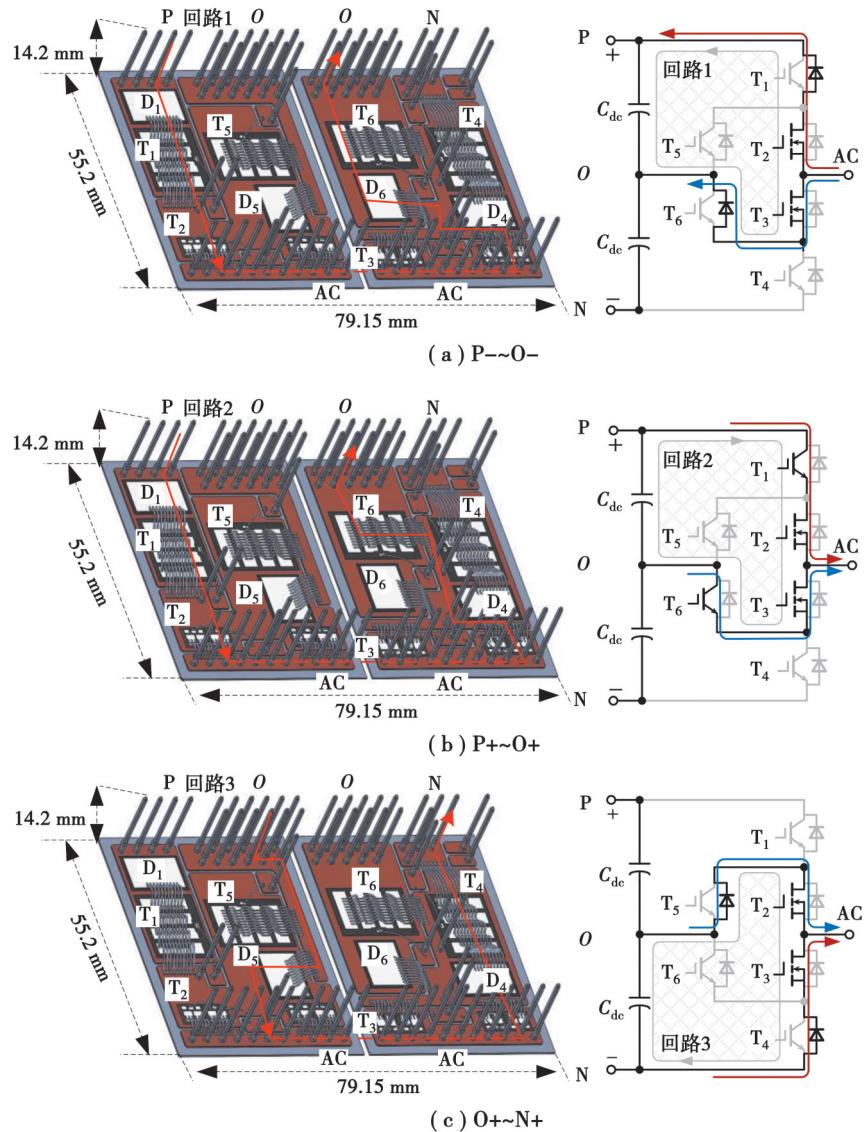

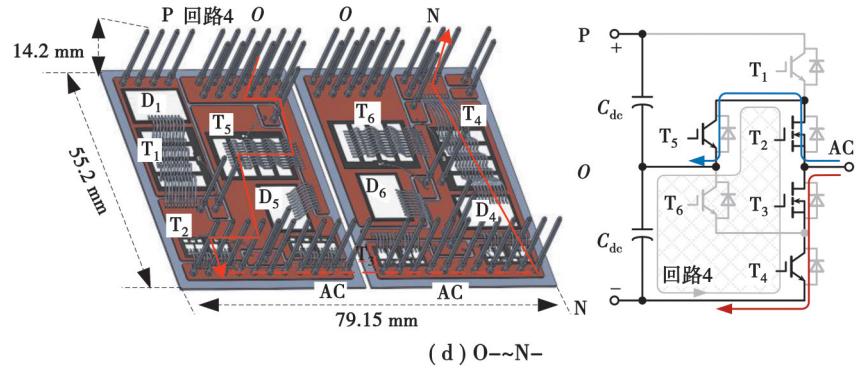

文中基于三电平换流回路原理, 提出寄生电感的优化设计方法, DBC 布局如图 7 所示。

图7 混合SiC/Si ANPC功率模块的DBC布局

Fig. 7 DBC layouts of hybrid SiC/Si ANPC power module

图中箭头所指的方向为从正极P到中点O或者从中点O到负极N的一条功率回路,AC为交流输出侧。文中采用P-Cell/N-Cell的原理,缩短回路中路径,减小键合线长度,减小回路自感;采用磁场相消的原理,正极P到AC端导体与AC端到中点O导体一对导体,或中点O到AC端导体与AC端到负极N导体一对导体流过电流相反,导体之间的耦合电感抵消导体的自感,从而减小回路互感。

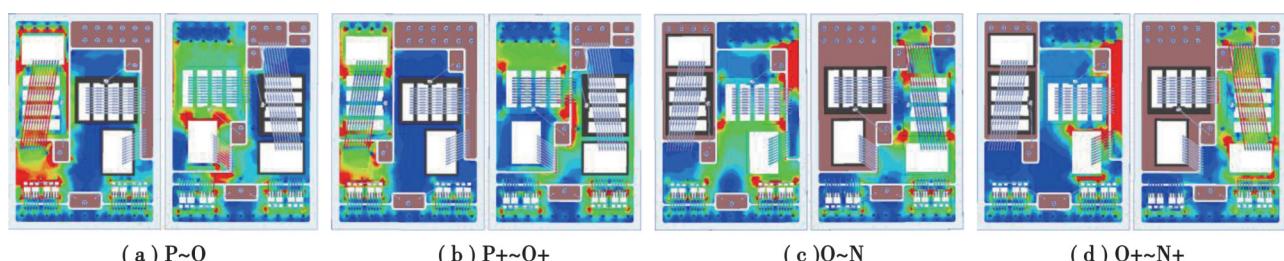

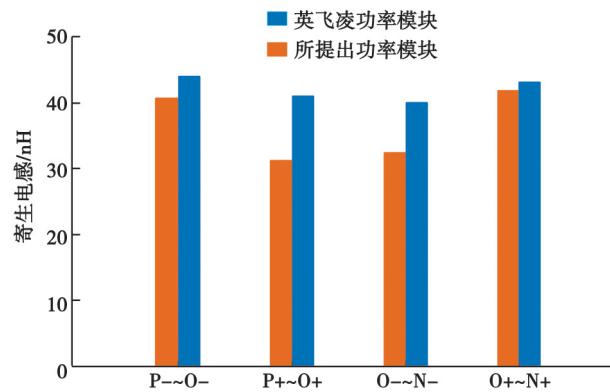

根据混合功率模块寄生电感模型,采用有限元分析方法,使用ANSYS Q3D软件,对三电平ANPC拓扑的4个换流回路进行仿真,仿真结果如图8~10所示。将流过每段导体的电流注入到一个Source,基于ANSYS Q3D提取寄生电感。由图8~10可知,4个换流回路寄生电感分布较为均衡,且文中功率模块回路寄生电感均小于英飞凌模块。此外,文中功率模块最小换流回路寄生电感为31 nH,而英飞凌功率模块最小换流回路寄生电感为39.8 nH,即文中模块比英飞凌模块寄生电感小22.1%。综上所述,文中混合功率模块有效降低换流回路寄生电感。

图8 英飞凌功率模块的FEA仿真结果

Fig. 8 FEA simulation results of the Infineon power module

图9 文中功率模块的FEA仿真结果

Fig. 9 FEA simulation results of the proposed power module

图 10 文中功率模块与英飞凌功率模块的寄生电感对比

Fig. 10 Comparison of parasitic inductances between proposed and Infineon power modules

### 3 实验验证与结果分析

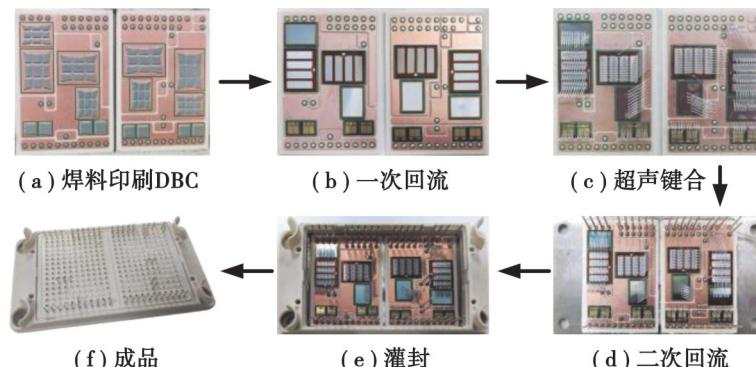

#### 3.1 混合 SiC/Si ANPC 功率模块的制作流程

为验证上述方案的可行性及优化效果, 研制 EASY 3B 封装的混合功率模块样机, 如图 11 所示。混合功率模块各个部件的尺寸、厚度和材料如表 2 所示。其中, SiC MOSFET 芯片采用瞻芯电子 IV2Q12017BA(100 A/1 200 V, 17 mΩ)、Si IGBT 和 FRD 芯片采用森未科技 SC193N12TFI8(200 A/1 200 V) 和 D12N200VA(400 A/1 200 V), 高温焊料选用熔点为 217 °C 的 SAC305。硅凝胶采用 SilGel 612 A/B, 由 1:1 混合 A 液和 B 液, 加热固化而得。

图 11 文中 ANPC SiC/Si 功率模块的制作流程

Fig. 11 Step-by-step process of proposed ANPC hybrid SiC/Si power module

表 2 混合 SiC/Si 功率模块各部件的相关参数

Table 2 Parameters of components for hybrid SiC/Si power module

| 部件        | 尺寸/mm <sup>2</sup> | 厚度/高度/mm | 材料                             |

|-----------|--------------------|----------|--------------------------------|

| MOSFET 芯片 | 5.0×5.0            | 0.18     | SiC                            |

| IGBT 芯片   | 16.0×12.1          | 0.12     | Si                             |

| FRD 芯片    | 12.1×8.7           | 0.20     | Si                             |

| 基板        | 111.4×60.0         | 3.00     | AlSiC                          |

| DBC 上层铜   | 51.2×35.0          | 0.30     | Cu                             |

| DBC 下层铜   | 55.2×39.0          | 0.38     | Al <sub>2</sub> O <sub>3</sub> |

#### 3.2 混合 SiC/Si ANPC 功率模块的电学性能

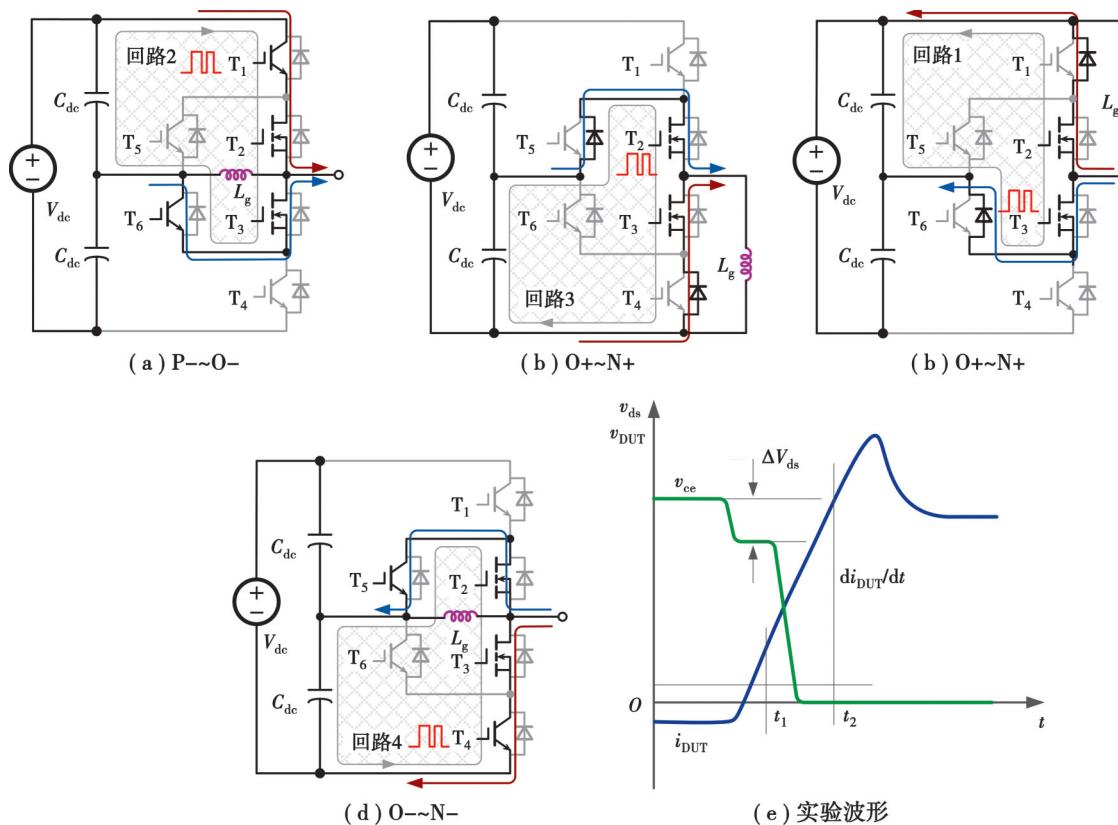

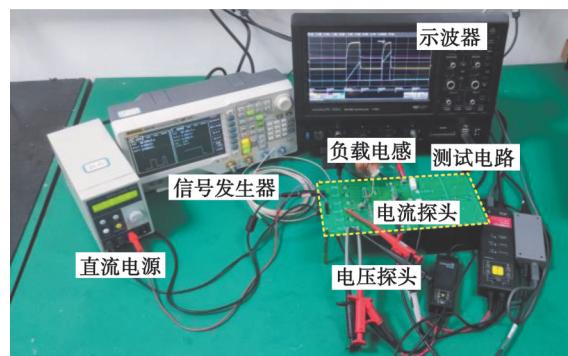

采用双脉冲测试电路, 评估文中功率模块的电气性能。但是, 不同于传统双脉冲测试, 在测量回路寄生

电感时,将处于该回路中的开关器件接入双脉冲信号的位置,并短接其余开关器件的栅极端子,以避免误导通,如图 12(a)~(d)所示。文中以 P~O~换流回路为例,采用 MOSFET 第二次开通暂态测量杂散电感,快速上升的  $di/dt$ 会在杂散电感上感应出  $\Delta V_{ds}$ 。这个过程中 MOSFET 电流迅速上升,由基尔霍夫电压定律可知,测量 MOSFET 电压  $V_{ds}$  等于母线电压  $V_{dc}/2$  减去杂散电感上的电压  $\Delta V_{ds}$ ,反映到 MOSFET 的开通电压波形就会出现一个缺口,如图 12(e)所示。因此,基于图 11(e)所示 ANPC 功率模块寄生电感测试原理,搭建如图 13 所示的寄生电感测试平台,以评估其电气特性。其中,采用电压差分探头测量电压  $v_{ds}$ ,采用罗氏线圈测量电流  $i_{DUT}$ ,采用示波器采集实验波形。直流侧电压  $V_{dc}$ 由直流电源提供,驱动板由可调开关电源供电,直流母线电容为薄膜电容。考虑到 ANPC 换流回路的复杂性,驱动板采用板卡形式设计,允许直接插入模块的驱动引脚,采用独立栅极驱动芯片,在每个开关管栅-源极之间施加 15 V/−5 V 的驱动电压。

图 12 ANPC SiC/Si 功率模块的寄生电感测试原理

Fig. 12 Test principle of parasitic inductance for proposed ANPC hybrid SiC/Si power module

图 13 ANPC SiC/Si 功率模块的寄生电感测试平台

Fig. 13 Test rig of parasitic inductance for proposed ANPC hybrid SiC/Si power module

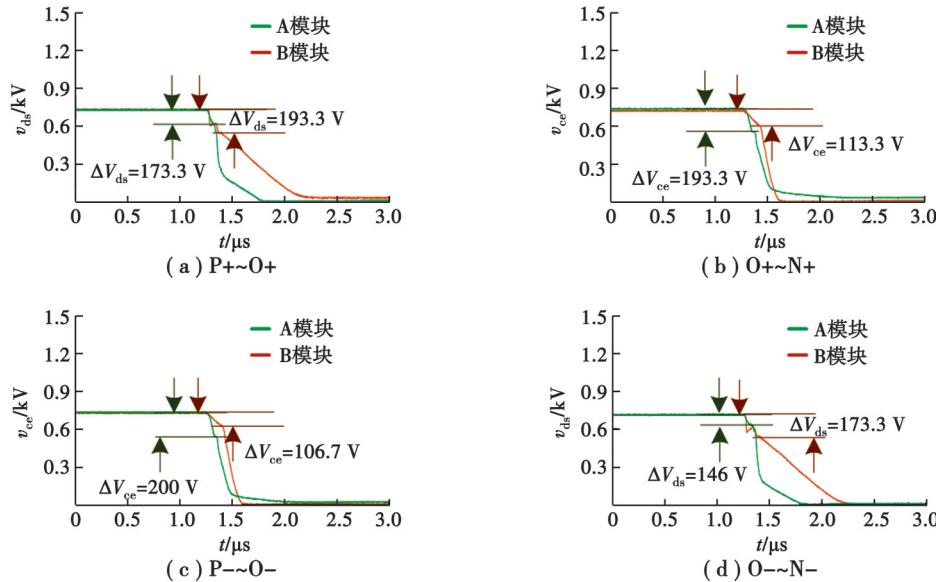

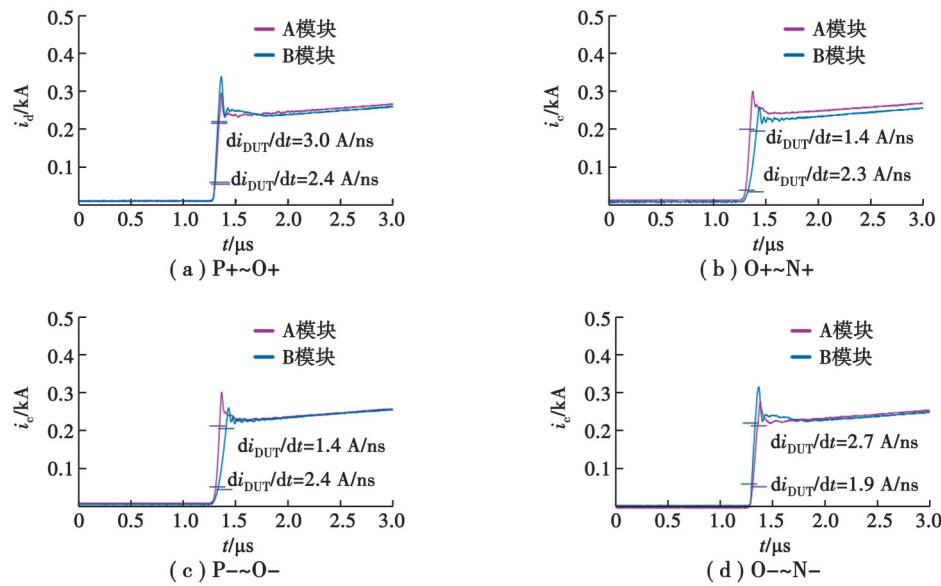

测量条件为: 直流母线电压 1 500 V、负载电流 200 A, 对标英飞凌功率模块, 文中功率模块在 4 个换流回路中的开关过程, 如图 14 和图 15 所示。将漏源电压变化量和电流的变化量计算结果统计在表 3 中, 根据式(8)计算出每个换流回路的寄生电感  $L_{\text{Loop}}$ , 该值包括了完整换流回路, 涵盖了功率端子之间的寄生电感。因此, 为了得到功率模块内部换流回路寄生电感  $L_{\text{g}}$ , 应该由整个换流回路寄生电感  $L_{\text{Loop}}$  和功率端子母排的寄生电感  $L_{\text{Bus}}$  相减得出。

$$L_{\text{Loop}} = \Delta V_{\text{ds}} / (\text{di/dt}) \quad (8)$$

图 14 文中功率模块与英飞凌功率模块  $v_{\text{ds}}/v_{\text{ce}}$  测试结果

Fig. 14 Comparison of measured  $v_{\text{ds}}/v_{\text{ce}}$  with proposed and Infineon power modules

图 15 文中功率模块与英飞凌功率模块  $i_{\text{d}}/i_{\text{c}}$  测试结果

Fig. 15 Comparison of measured  $i_{\text{d}}/i_{\text{c}}$  with proposed and Infineon power modules

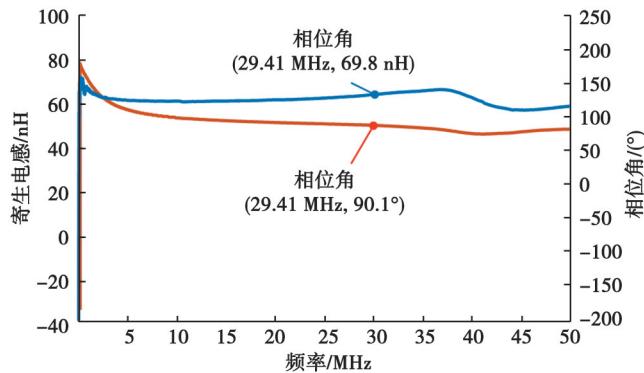

采用矢量网络分析仪 TD3615C, 测量功率端子母排的寄生电感, 如图 16 所示, 整个母排寄生电感为 69.8 nH。由于每个换流回路中, 母排仅有一半接入到回路中, 为了计算模块内部的寄生电感, 需要减去一半的母排寄生电感得到  $L_{\text{g}}$ , 因此在相同电压电流相同测试条件下, 文中功率模块(图 14~15 中 B 模块)内部最小

回路寄生电感为 29.2 nH, 低于英飞凌模块(图 14 和图 15 中 A 模块)内部最小回路寄生电感 37.2 nH, 减小 21.5%。同时, 将 2 个功率模块仿真寄生电感  $L'_o$  统计在表 3 中, 利用 ANSYS Q3D 软件仿真与实验数据误差在 12.5%, 验证了寄生电感模型的有效性。

图 16 母排寄生电感

Fig. 16 Busbar parasitic inductance

表 3 文中功率模块与英飞凌功率模块的寄生电感参数

Table 3 Inductance parameters of proposed and Infineon power modules

| 功率模块 | 参数                          | P+~O+ | O+~N+ | P-~O- | O-~N- |

|------|-----------------------------|-------|-------|-------|-------|

| A 模块 | $\Delta V_{CE}/V$           | 173.3 | 193.3 | 200.0 | 146.7 |

|      | $di_c/dt/(A \cdot ns^{-1})$ | 2.4   | 2.3   | 2.4   | 1.9   |

|      | $L_{oLoop}/nH$              | 72.2  | 84.0  | 83.3  | 77.2  |

|      | $L_o/nH$                    | 37.2  | 49.0  | 48.3  | 42.2  |

| B 模块 | $L'_o/nH$                   | 40.8  | 42.9  | 43.8  | 39.8  |

|      | $\Delta V_{CE}/V$           | 193.3 | 113.3 | 106.7 | 173.3 |

|      | $di/dt/(A \cdot ns^{-1})$   | 2.9   | 1.4   | 1.4   | 2.7   |

|      | $L_{oLoop}/nH$              | 66.7  | 80.9  | 76.2  | 64.2  |

|      | $L_o/nH$                    | 31.7  | 45.9  | 41.2  | 29.2  |

|      | $L'_o/nH$                   | 31.0  | 41.6  | 40.7  | 32.2  |

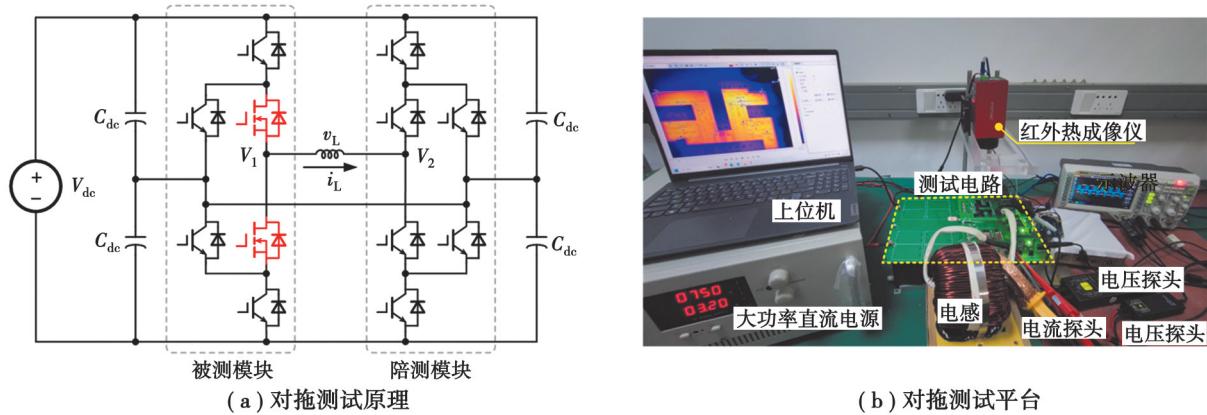

### 3.3 混合 SiC/Si ANPC 功率模块的热学性能

为了测试功率模块在实际工作时的最大结温和温度分布情况, 按照如图 17(a)所示原理, 设计如图 17(b)所示对拖平台, 以实现功率模块内部的功率循环, 并测量各个器件在运行时的结温。交流侧  $v_L$  和电感

图 17 对拖测试原理及平台

Fig. 17 Principle and platform of the experiment

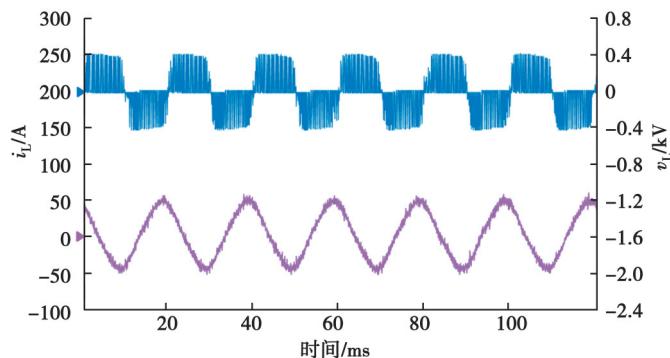

电流  $i_L$  如图 18 所示。

图 18 对拖测试波形

Fig. 18 Face-to-face converter towed experimental waveform

对拖测试平台由 PCB 测试板、2 个功率模块、母排电容、DSP 控制器、驱动和散热器构成。功率模块底部抹有导热系数为  $5 \text{ W}/(\text{m}\cdot\text{K})$  的导热硅脂, 散热器采用了 2 个 24 W 的风扇加强散热效果。采用红外热成像仪实时采集温度分布数据, 具体实验装置如表 4 所示。

表 4 混合 SiC/Si ANPC 功率模块的对拖实验参数

Table 4 Parameters of test rig for ANPC hybrid SiC/Si power module

| 设备      | 参数                                      |

|---------|-----------------------------------------|

| 功率模块    | 额定电压电流 200 A/1 200 V                    |

| 红外热成像仪  | 温度设置为默认值 20 °C                          |

| 大功率直流电源 | 输出电压 0~1 000 V, 输出电流 0~10 A, 输出功率 10 kW |

| 电感      | 5 mH                                    |

| 直流母线电容  | 薄膜电容 195 μF/1 200 V                     |

| 风冷散热器   | 2 个 24 W 风扇, 转速 15 000 rad/s            |

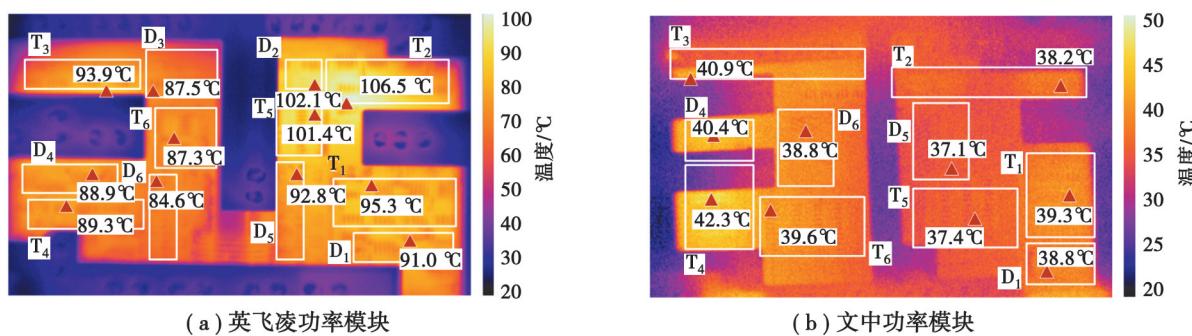

在 750 V/52 A 的实验测试条件下, 测量 2 种模块中各芯片的结温, 初始温度为室温 25 °C。直流侧母线电压  $V_{dc}$  为 750 V, 交流侧  $v_L$  的幅值 400 V、周期 0.02 s, 符合调制波设定的 50 Hz 周期, 电感电流  $i_L$  波形基本为正弦波, 因为有 2 μs 的死区设定, 在过零点存在畸变。英飞凌模块与文中模块在实验条件下的各芯片的结温如图 19 所示。相比于英飞凌模块, 文中混合 SiC MOSFET 型 ANPC 模块最高结温在芯片  $T_4$  处, 为 42.3 °C, 整个模块最大温差为 5.2 °C。而英飞凌模块最高结温在芯片  $T_2$  处, 为 106.5 °C, 整个模块最大温差为 21.9 °C。这表明文中模块具有较好的热分布特性。

图 19 文中功率模块与英飞凌模块对拖测试结果对比

Fig. 19 Comparison of experimental results between proposed and Infineon power modules

### 3.4 光储功率模块定性比较

文中给出了几种光储功率模块方案的定性比较,如表5所示。表中评分采用1~5分数字的形式,分数越高表示该项特征越明显。除全Si型两电平外,所有功率模块均表现出优异的热性能。然而,文中设计的混合SiC/Si型ANPC光储功率模块相比上述其他拓扑的功率模块具有效率高、功率密度大、成本与性能好的优势。通过灵活的中点钳位控制,ANPC拓扑显著降低了开关损耗和导通损耗,同时利用Si和SiC器件的混合配置,在性能和成本之间达到了良好的折中。此外,其更优的热分布特性,使其在高效率和高功率密度场景中具有明显竞争力,且复杂度相较于(active neutral point clamped, ANPC)五电平中性点钳位(5-level neutral point clamped, 5L-NPC)和飞跨电容中性点钳位(flying capacitor neutral point clamped, FC-NPC)更低。

表5 光储功率模块的定性比较

Table 5 Qualitative comparison of photovoltaic and energy storage power modules

| 类型           | 参考文献   | 功率损耗 | 控制难度 | 散热需求 | 封装复杂度 | 效率 | 成本 |

|--------------|--------|------|------|------|-------|----|----|

| 两电平(Si)      | 文献[25] | 4    | 1    | 2    | 1     | 2  | 2  |

| 两电平(SiC)     | 文献[25] | 3    | 1    | 2    | 1     | 3  | 4  |

| NPC(Si/SiC)  | 文中方法   | 3    | 4    | 3    | 3     | 4  | 4  |

| ANPC(Si/SiC) | 文中方法   | 2    | 4    | 3    | 3     | 5  | 4  |

| 5L-NPC       | 文献[26] | 1    | 5    | 5    | 5     | 5  | 5  |

| FC-NPC       | 文献[27] | 1    | 5    | 5    | 5     | 5  | 4  |

## 4 结论

ANPC因其高效率、良好的输出总谐波失真和低共模噪声而被广泛应用于光储发电系统。然而,传统ANPC拓扑采用全Si器件,限制了效率的进一步提升,直接引入SiC器件,传统模块功率回路中较高的寄生电感会引发严重的电压过冲、振荡和热分布不均衡等问题。基于损耗模型实现功率模块热优化,基于寄生电感模型实现换流回路寄生电感优化,并通过大量不同工况实验结果,验证了基于构建模型方法电热优化设计的可行性和有效性,得到以下结论:

1)为解决混合功率模块损耗不均衡问题,提出基于混合SiC MOSFET型ANPC功率模块损耗模型。综合考虑损耗均衡、效率、损耗大小、成本等因素,混合SiC MOSFET型ANPC三电平拓扑最适合光储系统,为混合SiC MOSFET型ANPC拓扑功率模块热设计提供参考。

2)为解决SiC器件引入ANPC拓扑后,长换流回路过程中产生的电压过冲问题,基于寄生电感模型,采用P-Cell/N-Cell原理减小自感,采用磁场相消原理减小互感的优化方法,降低模块回路寄生电感,为混合SiC MOSFET型ANPC拓扑功率模块电设计提供参考。

3)相对于商业化光储功率模块的设计,优化功率模块的电热性能,仿真与实验结果表明:基于模型构建的损耗均衡和低寄生电感优化设计,在不同工况下能够使功率模块结温降低60.3%,温差减小16.7 °C,回路寄生电感降低21.5%,为混合SiC/Si型ANPC拓扑的功率模块低感-热均衡设计提供新的设计方法和研究思路。

## 参考文献

- [1] Chen Z B, Huang A Q. Extreme high efficiency enabled by silicon carbide (SiC) power devices[J]. Materials Science in Semiconductor Processing, 2024, 172: 108052.

- [2] 曾正,邵伟华,胡博容,等. SiC器件在光伏逆变器中的应用与挑战[J]. 中国电机工程学报, 2017, 37(1): 221-233.

- Zeng Z, Shao W H, Hu B R, et al. Chances and challenges of photovoltaic inverters with silicon carbide devices[J].

- Proceedings of the CSEE, 2017, 37(1): 221-233. (in Chinese)

- [ 3 ] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947-4962.

- Wang L L, Zhao C, Zhang T Y, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electrotechnical Society, 2023, 38(18): 4947-4962. (in Chinese)

- [ 4 ] Belkhode S, Shukla A, Doolla S. A family of Si and SiC devices-based short commutation loop hybrid-NPC rectifiers[J]. IEEE Transactions on Industry Applications, 2024, 60(3): 4899-4909.

- [ 5 ] Wang J P, Chen W J, Wang L L, et al. A transient 3-D thermal modeling method for IGBT modules considering uneven power losses and cooling conditions[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(4): 3959-3970.

- [ 6 ] 罗丹, 陈民铀, 赖伟, 等. 大功率 MMC 系统中子模块 IGBT 状态监测系统设计方法[J]. 重庆大学学报, 2023, 46(11): 102-118.

- Luo D, Chen M Y, Lai W, et al. Design method of IGBT module condition monitoring system for submodule in high power MMC system[J]. Journal of Chongqing University, 2023, 46(11): 102-118. (in Chinese)

- [ 7 ] Zeng Z, Zhang X, Blaabjerg F, et al. Stepwise design methodology and heterogeneous integration routine of air-cooled SiC inverter for electric vehicle[J]. IEEE Transactions on Power Electronics, 2020, 35(4): 3973-3988.

- [ 8 ] Mu W, Wang L L, Wang B Y, et al. Direct integration of optimized phase-change heat spreaders into SiC power module for thermal performance improvements under high heat flux[J]. IEEE Transactions on Power Electronics, 2022, 37(5): 5398-5410.

- [ 9 ] Kjærsgaard B F, Liu G, Aunborg T S, et al. Discovery of loss imbalance in SiC half-bridge power modules – analysis and validations[J]. IEEE Transactions on Power Electronics, 2024, 39(5): 5806-5819.

- [ 10 ] 徐盛友, 陈民铀, 冉立, 等. 新能源转换系统功率模块驱动可靠性分析与试验[J]. 重庆大学学报, 2013, 36(10): 42-47.

- Xu S Y, Chen M Y, Ran L, et al. Analysis and experiment for reliability of power module driving circuit in renewable energy conversion system[J]. Journal of Chongqing University, 2013, 36(10): 42-47. (in Chinese)

- [ 11 ] Emon A I, Yuan Z, Mirza A B, et al. 1200 V/650 V/160 A SiC Si IGBT 3L hybrid T-type NPC power module with enhanced EMI shielding[J]. IEEE Transactions on Power Electronics, 2021, 36(12): 13660-13673.

- [ 12 ] Guan Q X, Li C S, Zhang Y, et al. An extremely high efficient three-level active neutral-point-clamped converter comprising SiC and Si hybrid power stages[J]. IEEE Transactions on Power Electronics, 2017, 33(10): 8341-8352.

- [ 13 ] Zhang L, Lou X T, Li C S, et al. Evaluation of different Si/SiC hybrid three-level active NPC inverters for high power density [J]. IEEE Transactions on Power Electronics, 2020, 35(8): 8224-8236.

- [ 14 ] Qin Y, Albano B, Spencer J, et al. Thermal management and packaging of wide and ultra-wide bandgap power devices: a review and perspective[J]. Journal of Physics D: Applied Physics, 2023, 56(9): 093001.

- [ 15 ] Li Z J, Wang J, Ji B, et al. Power loss model and device sizing optimization of Si/SiC hybrid switches[J]. IEEE Transactions on Power Electronics, 2020, 35(8): 8512-8523.

- [ 16 ] Li Z J, Wang J, He Z Z, et al. Performance comparison of two hybrid Si/SiC device concepts[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 42-53.

- [ 17 ] Zhang D, He J B, Pan D. A megawatt-scale medium-voltage high-efficiency high power density “SiC Si” hybrid three-level ANPC inverter for aircraft hybrid-electric propulsion systems[J]. IEEE Transactions on Industry Applications, 2019, 55(6): 5971-5980.

- [ 18 ] Yuan X B, Laird I, Walder S. Opportunities, challenges, and potential solutions in the application of fast-switching SiC power devices and converters[J]. IEEE Transactions on Power Electronics, 2021, 36(4): 3925-3945.

- [ 19 ] He J B, Zhang D, Pan D. PWM strategy for MW-scale “SiC Si” ANPC converter in aircraft propulsion applications[J]. IEEE Transactions on Industry Applications, 2021, 57(3): 3077-3086.

- [ 20 ] Huang Z Z, Chen C, Xie Y, et al. A high-performance embedded SiC power module based on a DBC-stacked hybrid packaging structure[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 351-366.

- [ 21 ] Chen C, Chen Y, Li Y X, et al. An SiC-based half-bridge module with an improved hybrid packaging method for high power density applications[J]. IEEE Transactions on Industrial Electronics, 2017, 64(11): 8980-8991.

- [22] Lyu X T, Tian X Y, Li H, et al. Design of a lightweight low inductance power module with ceramic baseplates[C]//2020 IEEE Applied Power Electronics Conference and Exposition (APEC). New Orleans, LA, USA. IEEE, 2020: 2782-2787.

- [23] Yuan Z, Deshpande A, Narayanasamy B, et al. Design and evaluation of A 150 kVA SiC MOSFET based three level TNPC phase-leg PEBB for aircraft motor driving application[C]//2019 IEEE Energy Conversion Congress and Exposition (ECCE). . Baltimore, MD, USA. IEEE, 2019: 6569-6574.

- [24] Wang Z J, Wu Y H, Mahmud M H, et al. Busbar design and optimization for voltage overshoot mitigation of a silicon carbide high-power three-phase T-type inverter[J]. IEEE Transactions on Power Electronics, 2021, 36(1): 204-214.

- [25] 李晓玲,曾正,陈昊,等. SiC、Si、混合功率模块封装对比评估与失效分析[J]. 中国电机工程学报, 2018, 38(16): 4823-4835, 4988.

- Li X L, Zeng Z, Chen H, et al. Comparative package evaluation and failure mode analysis of SiC, Si, and hybrid power modules[J]. Proceedings of the CSEE, 2018, 38(16): 4823-4835, 4988. (in Chinese)

- [26] Li W H, Hu J W, Hu S J, et al. Capacitor voltage balance control of five-level modular composited converter with hybrid space vector modulation[J]. IEEE Transactions on Power Electronics, 2018, 33(7): 5629-5640.

- [27] Sadigh A K, Dargahi V, Corzine K A. Analytical determination of conduction and switching power losses in flying-capacitor-based active neutral-point-clamped multilevel converter[J]. IEEE Transactions on Power Electronics, 2016, 31(8): 5473-5494.

(编辑 詹燕平)