Dec. 2005 Vol. 28 No. 12

文章编号:1000-582X(2005)12-0065-04

# 多进制正交扩频系统中软信息提取电路的实现:

刘 晓 明,吴 皓 威,欧 静 兰 (重庆大学通信工程学院,重庆 400030)

摘 要:在相干多进制正交扩频通信系统中,需要对多路匹配滤波器输出信号进行最大值判决,以利于后级的信道译码. 从对数似然比(LLR)出发,提出了一种适用于多进制扩频系统的次最优的软信息提取方法,并仿真验证了该方法在 AWGN 信道中的性能,最后讨论了在 FPGA 上实现软信息提取的电路结构. 实践表明,这种次最优的软信息提取方法简单实用,便于 FPGA 实现,并能够有效节约硬件资源.

关键词:多进制正交扩频;软信息;可信信息;软判决

中图分类号:TN914

文献标识码:A

多进制正交扩频(M-ary Orthogonal Spread Spectrum)系统<sup>[1]</sup>是利用一个正交扩频序列传输  $\log_2 M$  (M 为进制数)比特信息的扩频系统. 该系统较直接序列扩频系统更能有效地解决传输带宽与处理增益之间的矛盾,并已经被应用于 IS -95、无线分组网等许多领域.

为提高数字通信系统性能,通常采用软判决方式做数字调制的解调输出,提供给信道译码器,以得到比硬判决高约 3 dB 的信噪比<sup>[2]</sup>. 特别是在维特比算法(Viterbi Algorithm, VA)中,软判决译码器不仅有额外的增益,而且并不比硬判决译码器复杂. 软判决译码需要对解调器的输出的电压进行分层和量化,获得每个码元的可信信息,即软信息.

在相干多进制正交扩频系统中,为了便于随后的 软 VA 译码,需要从  $M(M=2^k)$  路相关积分的输出中提取每个比特的软信息. 文献[1]讨论了多进制正交扩频系统和软判决方案,文献[3] 提出了一种针对 64QAM 解调信号 I、Q 两路的均匀量化并提取软信息的方法,文献[4]研究了基于单载波和多载波的编码调制(Bit-Interleaved Coded Modulation, BICM)系统的

软判决译码所需的软信息的提取. 但上述都不曾考虑 多路信号输出的软信息提取的算法,特别是没有针对 多进制正交扩频系统的软信息提取电路的论述. 而文 献[5]用传统对数似然比(Log-Likelihood Ratio, LLR) 的方法能够计算软判决信息,但由于复杂度高而无法 实际应用.

考虑到多进制正交扩频系统的特殊性,并兼顾实现的复杂度,从对数似然比出发,笔者提出了一种适用于多进制正交扩频系统的软判决信息的提取算法,并讨论了该算法在电路实现上的相关问题.

#### 1 LLR 提取软信息方案

在多进制正交扩频通信系统中,发送端信息经过 卷积编码和深度交织之后,由连续的  $K = \log_2 M(M)$  为进制数) 个编码数据  $d_i(j=0,1,\cdots,K-1;d_i\in(0,1))$  构成一个 K 比特的码字  $D,D\in(0,1,\cdots,M-1)$ ,由 D 选择输出的扩频码波形为  $C'(i=D,i\in(0,1,\cdots,M-1))$ ,C' 是由  $\pm 1$  构成的 N 维伪随机码序列波形. 经过 AWGN 信道,叠加一个 N 维的零均值且双边谱为  $N_0/2$  高斯白噪声,接收信号为 R.

<sup>\*</sup> 收稿日期:2005-07-12

基金项目:云南省省院省校科技合作计划项目(24031)

设发送码字是等概的, $G_j^0$  表示那些  $d_j = 0$  的码字  $\{C^i\}$  的集合,记作  $C_{(0)}^i \in G_j^0$ , $G_j^1$  表示那些  $d_j = 1$  的码字  $\{C^i\}$  的集合,记作  $C_{(1)}^i \in G_j^1$ ,则关于比特  $d_j$  的对数似然比(LLR)可以写做:

$$\Lambda_{j} = \Lambda(d_{j}) = \ln \sum_{C' \in C_{j}^{i}} P(R \mid C^{i}) - \ln \sum_{C' \in C_{j}^{0}} P(R \mid C^{i}),$$

(1)

其中,

$$P\{R/C^i\} = (\frac{1}{\sqrt{\pi N_0}})^N \exp(-\frac{|R-C^i|^2}{N_0}).$$

(2)

文献[5]给出了一种按照  $\Lambda_i$  计算可信信息的方法,但是其复杂度随着软信息量化位数的增加而成指数规律增加,不利于电路实现.

### 2 次最优的软信息提取方案

针对上述判决情况提出了一种次优的计算软信息的方法,可以极大地减少运算次数和复杂度,利于电路实现. 利用如下的近似关系<sup>[6]</sup>:

$$\ln\left(\sum_{k=1}^{N} \delta_{k}\right) \approx \ln\left(\max_{k \in \{1,2,\cdots,N\}} \{\delta_{k}\}\right) , \qquad (3)$$

式(3)中 $\max_{k \in (1,2,\cdots,N)} \{\delta_k\}$ 表示取 $\delta_k$ 中的最大值. 式(1)可以变为:

$$\Lambda_{j} \approx \ln\left[\max_{C^{i} \in C_{j}^{i}} P(R \mid C^{i})\right] - \ln\left[\max_{C^{i} \in C_{j}^{0}} P(R \mid C^{i})\right].$$

(4)

**将式(2)带人式(4)可得:**

$$\Lambda_{j} = \frac{1}{N_{0}} (\max_{C' \in C_{j}^{i}} | R - C_{(0)}^{i} |^{2} - \max_{C' \in C_{j}^{i}} | R - C_{(1)}^{i} |^{2}) - \frac{N}{2} \ln(\pi N_{0}) = \Lambda'_{j} + A_{\text{const}},$$

(5)

式(5)中, $A_{\text{const}} = -\frac{N}{2}\ln(\pi N_0)$ 为常数, $\Lambda'_j = \frac{1}{N_0}$  ·  $(\max_{C' \in \mathcal{C}_j^i} |R - C_{(0)}^i|^2 - \max_{C' \in \mathcal{C}_j^i} |R - C_{(1)}^i|^2)$ ,其中 $|R - C_{(0)}^i|^2$ 、 $|R - C_{(1)}^i|^2$ 均表示接收波形序列 R 和本地伪码序列  $C^i$  之间的欧式度量.

在 AWGN 信道中,若每路信号  $C_{(0)}$ 和  $C_{(1)}$ 具有相同的能量,即 $|C_{(0)}|^2 = |C_{(1)}|^2$ ,则欧式度量等价于相关度量<sup>[7]</sup>,那么:

$$\Lambda'_{j} = \frac{2}{N_{0}} (\max_{C' \in C'_{j}} R \cdot C'_{(1)} - \max_{C' \in C'_{j}} R \cdot C'_{(0)}) , \quad (6)$$

式(6) 中  $R \cdot C^i_{(1)}$ ,  $R \cdot C^i_{(0)}$  分别表示码字 D 的第 j 位为 1 或 0 的相关匹配滤波器的输出.

在相干多进制正交扩频系统接收端,与码字  $D \in (0,1,\cdots,M-1)$ 对应各组 PN 码  $C^i$  的相关匹配滤波器的输出设为 $\{Y_0,Y_1,\cdots,Y_i,\cdots,Y_{M-1}\}$ ,即  $Y_i=R\cdot C^i$ ,其

中 $i = D, i \in (0,1,\dots,M-1)$ . 根据码字 D 中第j 比特的 d, 取值对 D 进行如下分组:

$$g_i^{(1)} = \{ \forall D, d_i = 1 \},$$

$g_i^{(0)} = \{ \forall D, d_i = 0 \}.$  (7)

则第 j 比特的软判决信息输出为:

$$S_{j} = \max_{D \in g_{i}^{(1)}} | Y_{i}| - \max_{D \in g_{i}^{(0)}} | Y_{i}|.$$

(8)

可以归一化为:

$$\hat{S}_{j} = (\max_{D \in s_{j}^{(1)}} | Y_{i}| - \max_{D \in s_{j}^{(0)}} | Y_{i}|) / MAX_{j}, \quad (9)$$

式(9)中

$$MAX_{j} = \max(\max_{D \in g(1)} | Y_{i}|, \max_{D \in g(0)} | Y_{i}|). \quad (10)$$

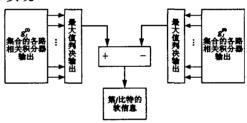

$\hat{S}_j$ 表示  $d_j$  判为 1 或 0 的可信度.  $\hat{S}_j$ 越接近 + 1,说明  $d_j$  被判决为 1 的可能性越大;  $\hat{S}_j$ 越接近 - 1,说明  $d_j$  被判决为 0 的可能性越大. 该方法的具体实现结构如图 1 所示,显然,这种方法比式(1) 所述的对数似然比方法更利于实现.

图 1 次最优软信息提取的原理结构

## 3 仿真对比

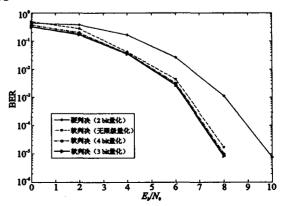

利用 Matlab/Simulink 软件仿真验证了采用上述方法提取软信息的可行性,并对比了多进制正交扩频系统在 AWGN 信道中采用软判决与硬判决的误码性能,如图 2 所示. 仿真采用 16 进制扩频系统,扩频码码长为 64,卷积编码(2,1,7),考虑对软信息无限级量化(模拟值)和 16 电平均匀量化、8 电平均匀量化的情况.

图 2 AWGN 信道下软判决和硬判决的性能比较

从仿真结果可以看出:提取软信息的方法是可行的;AWGN 信道中,在相同误比特率的情况下,采用笔者提出的软信息提取方法进行软判决译码,比采用硬判决译码有近2 dB 的软判决增益,达到了文献[2]描述的最大软判决增益标准;软信息的8 电平、16 电平均匀量化的性能非常接近无限级量化,所以在工程实现时经常使用8 电平或16 电平均匀量化就能达到要求.

#### 4 软信息提取电路的 FPGA 实现

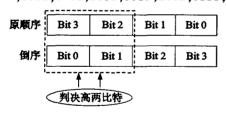

在 FPGA 上设计实现 16 进制扩频系统的软信息 提取电路时,需要根据图 3 所示的方法逐比特进行判 决,需要 4 组 16 信号最大值判决电路,共需要 56 个二 输入比较器和 4 个加法器,硬件成本较高.

经分析 4 组判决输出的特点,得到了一种新颖的判决电路结构.在电路中使用一个控制信号,在控制信号为低时,将信号按照支路号的二进制表示的正常顺序输出,即 0000,0001,0010,0011,0100,0101,0110,0111,1100,1101,1111;在控制信号为高时,将信号按照支路号的二进制倒序输出,即 0000,1000,0100,1100,0010,1010,0110,1110,0001,1001,0101,0111,1111.

图 3 4 Bit 软信息的判决示意图

在控制信号为低时,0~3、4~7、8~11、12~15 路信号分别由一个四输入的最大值判决电路进行判决输出最大值,高两比特(Bit 3、Bit 2)的软信息输出分别为:

$$S_{3} = \max\{\max(Y_{8}, Y_{9}, Y_{10}, Y_{11}), \max(Y_{12}, Y_{13}, Y_{14}, Y_{15})\} - \max\{\max(Y_{0}, Y_{1}, Y_{2}, Y_{3}), \max(Y_{4}, Y_{5}, Y_{6}, Y_{7})\}$$

(11)

$$S_{2} = \max\{\max(Y_{4}, Y_{5}, Y_{6}, Y_{7}), \max(Y_{12}, Y_{13}, Y_{14}, Y_{15})\} - \max\{\max(Y_{0}, Y_{1}, Y_{2}, Y_{3}), \max(Y_{8}, Y_{9}, Y_{10}, Y_{11})\}$$

(12)

在控制信号为高时,信号按照倒序输出到后续电路,低两比特(Bit 0、Bit 1)的软信息输出为:

$$S'_{3} = \max\{\max(Y'_{8}, Y'_{9}, Y'_{10}, Y'_{11}), \max(Y'_{12}, Y'_{13}, Y'_{14}, Y'_{15})\} - \max\{\max(Y'_{0}, Y'_{1}, Y'_{2}, Y'_{3}), \max(Y'_{4}, Y'_{5}, Y'_{6}, Y'_{7})\} =$$

$$\max\{\max\{Y_{1}, Y_{3}, Y_{5}, Y_{7}\}, \max\{Y_{9}, Y_{11}, Y_{13}, Y_{15}\}\} - \max\{\max\{Y_{0}, Y_{2}, Y_{4}, Y_{6}\}, \max\{Y_{8}, Y_{10}, Y_{12}, Y_{14}\}\} = S_{0}$$

(13)

$$S'_{2} = \max\{\max(Y'_{4}, Y'_{5}, Y'_{6}, Y'_{7}), \max(Y'_{12}, Y'_{13}, Y'_{14}, Y'_{15})\} - \max\{\max(Y'_{0}, Y'_{1}, Y'_{2}, Y'_{3}), \max(Y'_{8}, Y'_{9}, Y'_{10}, Y'_{11})\} = \max\{\max(Y_{2}, Y_{3}, Y_{6}, Y_{7}), \max(Y_{10}, Y_{11}, Y_{14}, Y_{15})\} - \max\{\max(Y_{0}, Y_{1}, Y_{4}, Y_{5}), \max(Y_{8}, Y_{9}, Y_{12}, Y_{13})\} = S_{1}$$

$$(14)$$

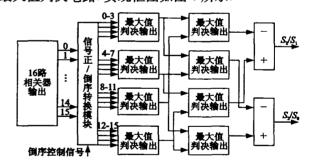

由式(11) - (14) 推导可知,16 路相关器输出信号首先输入信号正/倒序转换模块,通过倒序控制信号控制该模块的输出.在倒序控制信号为低时,正常输出高两比特的软信息  $S_3$  和  $S_2$ ;当倒序控制信号为高时,进行简单的信号交换,后续电路无须改动,倒序输出低两比特的软信息  $S_0$  和  $S_1$ . 为简化电路结构,不对输出软信息做归一化处理.

考虑到软信息提取过程中共用了大部分的比较器,这样整个判决电路所需的比较器数目大大减少,只需 16 个二输入比较器、2 个加法器和 8 个信号交换电路,故所用的 FPGA 硬件资源只是稍多于 1 组 16 信号最大值判决电路. 实现框图如图 4 所示.

图 4 软信息提取电路的实现框图

在宽带无线收发平台上,使用 QuartusII 中的 SignalTapII Logic Analyzer 从 FPGA 中提取数据验证了上述软信息提取方法和电路的可行性. 仿真结果如图 5.

| * Years        | 1536 (344 (195) 1560 (368 (1976 (1364 (1392 (466 (1466                                            |

|----------------|---------------------------------------------------------------------------------------------------|

| ■ INPUT_DATA   | (2h/Bh/1h/9h/0h/7h/0h/Dh/Ph/4h/5h) Ch Bh 6h/9h/Dh/8h/4h/8h                                        |

| 2-HARD         | (Dh(2h)Bh(1h(9h)(0h(7h)(0h)Dh(Ph)(4h)(5h)(Ch ) Bh (6h(9h)Dh(8h)(4h)                               |

| g. <b>9</b> 03 | (0)-1)6(-7)(5)(-7)(5)(4)(-7)(0)(1)(7)(6)(-7)(7)(0)(-1                                             |

| £- SO2         | 0 -8 -7 -6 -7 -5 -7 -7 -5 -7 -1 -8 -7 -1 -8 -7 -1 -1 -8 -7 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 |

| <b>₩ 8</b> 01  | (1)(0)(7)(4)(7)(6)(4)(4)(7)(1)(2)(7)(6)(8)(-1                                                     |

| ⊕ <b>SO</b> 0  | 0 (8) 6 (5) 7 (5) 4 (7) 6 (1) (2) 7 (6) (7) 7 (-1                                                 |

| imput_bit      |                                                                                                   |

| bard_bitout    |                                                                                                   |

图 5 软信息提取电路的实现结果

图 5 中, INPUT\_DATA 表示输入的信息数据, HARD 表示硬判决信息,SO3,SO2,SO1,SO0 分别表示 各信息比特的 16 电平量化的软信息,input\_bit 和 hard\_bitout分别表示输入比特流和硬判决数据的比特

流输出(发送码字和接收码字有一个码字周期的延时). 从图 5 可以看出,软信息能够准确反映各个比特的可信度信息.

#### 5 结 语

在 LLR 提取软信息的基础上,笔者提出了一种简单、实用的适用于多进制扩频系统的软信息提取方法,并仿真验证了该方法在 AWGN 信道中的性能,最后讨论了在 FPGA 上实现软信息提取电路时一种新颖的电路结构. 实践证明了该方法是有效的,而且简单快捷便于 FPGA 实现,还能有效节约硬件资源,很适合在工程中应用.

#### 参考文献:

[1] LEE J S, MILLER L E 著. CDMA 系统工程手册[M].

- 许西斌 译. 北京:人民邮电出版社,2001.

- [2] 王新梅,肖国镇.纠错码——原理方与法[M].西安: 西安电子科技大学出版社,1991.

- [3] WIM J VAN HOUTUM. Single Carrier Digital Terrestrial Television Broadcasting [J]. IEEE Transaction Broadcasting, 1997,43(4):403-411.

- [4] 徐波, 葛建华. 软判决译码中的软信息的提取[J]. 通信技术, 2002, (12):20-22.

- [5] PYNDIAH R M. Near-optimum Decoding of Product Codesblock Turbo Codes [J]. IEEE Transactions on Communications, 1998,46(8):1003-1010.

- [6] FOSSORIER M P C, BURKERT F, SHU LIN. On the Equivalence Between SOVA and Max-Log-MAP Decodings [J].

IEEE Communications Letters, 1998, 2(5):137-139.

- [7] PROAKIS J G. Digital Communication[M]. New York: McGrawhill, 1989.

# Implement of Extracting Circuit for Soft-information in M-ary Orthogonal Code Spread-spectrum System

LIU Xiao-ming, WU Hao-wei, OU Jing-lan

(College of Communication Engineering, Chongqing University, Chongqing 400030, China)

Abstract: In the coherent M-ary Orthogonal Code Spread-Spectrum System, the maximal value decision of the output signals from the multiple matched filters is needed before channel decoding. Based on the Log-likelihood Radio(LLR), a suboptimal soft-information extracting scheme in the M-ary Orthogonal Code Spread-spectrum System is proposed and the performance of the system in the AWGN channel is analyzed. Then the architecture of the system implemented on FPGA is presented. The practical results indicate that the scheme is effective and can be implemented on FPGA easily and conveniently.

Key words: M-ary orthogonal spread-spectrum; soft information; reliability information; soft-decision

(编辑 张 革)