VDMOS作为近年来开发的最重要的功率器件,在开关电源、DC转换、电机驱动控制等领域得到了十分广泛的运用[1-2]。目前N沟道VDMOS器件的研制在国内外均已经取得了重大突破[3-6],而P沟道VDMOS由于性能相对较弱且运用领域十分狭窄,国内外对其研究都极其匮乏。但相比于N沟道VDMOS,P沟道VDMOS器件在图腾柱式功率管组电路中,作为高压侧控制开关,有其独特的优势: P沟道VDMOS既不需要用于高压电平位移的电荷泵电路,也不存在高、低压开关控制信号同步的问题,在恶劣的电磁环境下具有不可替代的高可靠性优势[7]。笔者在项目前期所研制耐压-80 V的P沟道VDMOS器件[8]基础上,对一款

击穿电压超过-200 V,阈值电压-2.0 V~-4.0 V的P沟道VDMOS的元胞结构进行了研究,利用仿真软件Silvaco对其结构参数与电学性能的关系进行了讨论,并对其重点参数和工艺流程进行了仿真,为项目下一步的流片提供了有益参考。

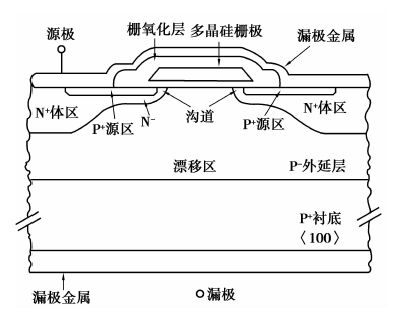

1、 P沟道VDMOS的结构设计高压大功率P沟道VDMOS器件有源区元胞通常采用图 1所示的平面(Planar)结构。与传统P沟道MOS器件类似,P沟道VDMOS器件也通过栅电压VG来控制器件工作。但与传统P沟道MOS器件所不同的是, 在图 1所示结构中N+阱区与P-外延层之间构成了一个寄生体二极管,当VG绝对值低于阈值电压Vth时,器件处于关断状态,源漏电压VDS将被完全被加载到该寄生体二极管2端,其击穿电压决定着器件的关键指标——击穿电压BVDS。为提高寄生体二极管的击穿电压,需要采用较厚的轻掺杂外延层,这样该寄生体二极管的PN结耗尽区将主要向外延层中延伸,使得绝大部分反偏电压由较厚的外延层承担,可以有效提高器件击穿电压。

|

图 1 P沟道VDMOS元胞剖面结构 Figure 1 The cross-section of P-channel VDMOS cell structure |

大功率VDMOS的另一个重要指标——导通电阻Ron则决定了器件的最大输出电流。通常它由元胞的布局、几何形状及尺寸、元胞密度及芯片面积等因素决定[9]。对于高压VDMOS的元胞,Ron主要由以下4部分构成(Chenming Hu模型[10])

| ${{R}_{\text{on}}}={{R}_{\text{cn}}}+{{R}_{A}}+{{R}_{\text{JEET}}}+{{R}_{EPi}},$ | (1) |

式中:RCh为沟道电阻,RA为栅氧化层下方的电荷积累层电阻,RJFET为颈区寄生结型场效应管电阻,REpi为外延层电阻。

对于高压VDMOS器件,随着BVDS的提高,Ron将成倍上升,这主要是其中REpi的分量迅速增加所致。在500 V以上的高压VDMOS器件中REpi甚至会占到Ron的80%以上[11],这不仅使器件热耗散功率大增,也限制了器件电流密度的进一步提高。虽然单纯提高元胞数量可以明显降低器件的整体导通电阻,但这会使栅电荷急剧增加,开关损耗变大。因此,在高压VDMOS器件的元胞设计中如何通过优化元胞结构设计以平衡BVDS与Ron这对矛盾,一直是设计的关键。

击穿电压决定了漂移区掺杂浓度NDft和厚度WDft的选取。此处为了方便讨论击穿的情况,引入临界电场Ec的概念:当PN结中电场强度达到临界电场Ec时,PN结将发生击穿[9-12],此时所对应的PN结反偏电压就是PN结的击穿电压。由于在反偏电压作用下VDMOS元胞耗尽区相互交叠,其击穿模型类似于平行平面结的雪崩击穿模型,因此漂移区掺杂浓度NDft和厚度WDft与Ec及BVDS之间的关系有如下公式

| ${{E}_{c}}={{\left( \frac{2q{{N}_{A}}B{{V}_{DS}}}{\varepsilon \text{si}} \right)}^{1/2}}\approx 8.5\times {{10}^{5}}BV_{_{DS}}^{-0.2}\text{V/cm,}$ | (2) |

| ${{\text{N}}_{\text{Dft}}}=\frac{4{{\varepsilon }_{\text{si}}}E_{c}^{2}}{9qB{{V}_{DS}}}\approx 1.9\times {{10}^{18}}BV_{_{DS}}^{-1.4}\text{V/c}{{\text{m}}^{\text{3}}}\text{,}$ | (3) |

| ${{W}_{\text{Dft}}}=\frac{3B{{V}_{DS}}}{2{{E}_{C}}}\approx 0.018BV_{_{DS}}^{1.2}\mu \text{m}。$ | (4) |

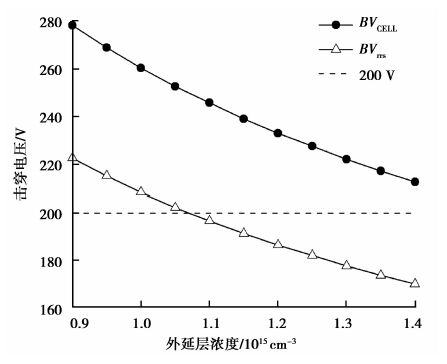

值得注意的是公式(2) 、(3) 、(4) 中击穿电压BVDS并非是器件所要求的击穿电压,这是由于在器件关断时,器件中环绕有源区的终端结构(junction termination structure, JTS)所承受的电场强度超过元胞区域的电场强度,使得终端结构的耐压值BVJTS最低可能仅有元胞的80%左右[3](见图 2中BVJTS曲线)。因此对于所设计器件,公式(2) 、(3) 、(4) 中BVDS应取设计指标的120%以上才能为整个器件留出足够的裕量[13-14]。

|

图 2 外延层掺杂浓度与击穿电压关系 Figure 2 Relationship between Concentration of epitaxial layer and breakdown voltage |

利用公式(2) 、(3) 、(4) 可以求出NDft和WDft的近似值分别为1.15×1015/cm3及10.39 μm,结合外延片生产工艺,通过Silvaco的器件特性仿真模块Atlas对外延层浓度与元胞击穿电压的关系进行仿真,得到图 2中BVCELL曲线,此时所估算器件终端结构的击穿电压为BVJTS曲线,可见要使器件整体达到设计所要求的击穿电压,实际流片时应选取外延片杂质浓度NEpi为1×1015/cm3,略低于公式(3) 所得值。虽然这样会导致器件Ron稍有增加,但为整个器件的击穿电压留出了足够余量。在确定外延层厚度WEpi时,除了由公式(4) 所得到的漂移区厚度WDft以外,还需加入N+体区的结深,以及由于工艺流程中扩散步骤导致的高浓度衬底杂质向轻掺杂外延层反扩散所损失的厚度,因此将WEpi参数定为25 μm。

阈值电压Vth是P沟道VDMOS的第3个重要指标。为方便讨论,在P沟道VDMOS器件的Vth公式[9]中将栅氧化层特征电容COX用电容定义式替换掉之后可得

| ${{\text{V}}_{th}}=\frac{\text{tox}}{\text{ }\!\!\varepsilon\!\!\text{ ox}}\sqrt{4{{\varepsilon }_{\text{si}}}T{{N}_{D}}\ln \left( \frac{{{N}_{D}}}{{{n}_{i}}} \right)}+\frac{2kT}{q}\ln \frac{{{N}_{D}}}{{{n}_{i}}}+\phi \text{ssi-}\frac{\text{toxQox}}{\text{ }\!\!\varepsilon\!\!\text{ ox}},$ | (5) |

式中:ψSSi是器件所采用P+型多晶硅栅与N-沟道之间的表面势。由式(5) 可知,Vth与栅氧化层厚度tOX及N-沟道区杂质最大浓度ND相关。对于实际生产中在栅氧化层中引入的氧化物电荷QOX,不妨假设其全部位于金属氧化物界面处,根据工艺条件选取氧化物电荷面密度QOX=1×1011/cm-2。栅氧化层厚度tOX应至少满足

|

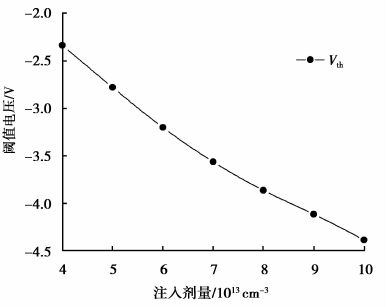

图 3 沟道区掺杂剂量与阈值电压关系 Figure 3 Relationship between dose of channel region and threshold voltage |

| $\text{tox}={{V}_{G}}/{{E}_{c,\text{ox}}},$ | (6) |

式中:Ec, OX为SiO2的击穿场强,一般为(5~10) ×106 V/cm,其具体取值与栅氧化层制备工艺水平决定,因此在工艺中需要特别留意栅氧化层质量。设计指标要求栅源电压的范围为-20~+20 V,由前面对阈值电压的分析,再结合流片生产线工艺水平,将栅氧化层厚度取800 A。

在工艺流程中,磷被注入外延层中形成N阱,并在高温作用下将其驱入栅氧化层下方,以完成沟道的制作。沟道区磷注入剂量与Vth之间关系见图 3。考虑到器件工作环境及工艺线水平,选取磷注入剂量为5×1013/cm2,此时提取的Vth为-2.78 V。

经仿真确定的器件部分关键参数由表 1给出。

| 表 1 设计器件部分关键参数 Table 1 The main parameters of designed device |

此外,为了使器件整体击穿电压达到设计标准,笔者在文献[15]所设计的-80 V的P沟道VDMOS所采用结终端结构基础上为该器件设计了如图 4所示的终端结构,采用了2组两级多晶硅-金属场板与单场限环复合的结构,其击穿电压达到-232 V,接近元胞击穿电压的90%,满足了设计的要求。此外,相比于其他同规格产品采用的双场限环结构[16-18],该结构节约了芯片面积,且不需要增加额外的工艺步骤。

|

图 4 设计结终端结构 Figure 4 The cross-section of junction termination in designed device |

以文献[8]所开发器件工艺为基础,借助Silvaco中的工艺仿真模块Athena,通过仿真为该P沟道VDMOS器件设计了一套平面双扩散非自对准工艺流程,以便调整和优化工艺流程中的步骤及参数。这种方式能很好地节约流片成本,并有助于分析实际工艺中可能出现的问题。最终得到的工艺流程和参数为:1) 外延片晶向<100>,其余参数参见表 1;2) 一次氧化,淀积Si3N4,用场氧化版光刻场氧窗口,二次氧化;3) 去除Si3N4和氧化层,三次氧化,用n+区版光刻n+区域,n+区域磷注入并退火;4) 去除有源区氧化层,栅氧化,淀积多晶硅并掺硼后退火,用POLY版光刻n区,以多晶硅为掩膜注入磷以实现沟道自对准;5) 用p+区版光刻p+区,注入硼后扩散,通过控制扩散时间控制沟道长度及进入栅氧化层下方的距离;6) 淀积磷硅玻璃,并用VIA版光刻引线孔,淀积源极金属;7) 用METAL版光刻金属层,合金化,淀积钝化层;8) 用PAD版光刻压焊点,退火;9) 背金属化。该工艺流程使用了包括了场氧化、n+区、POLY、p+区、VIA、METAL及PAD在内的一共7块光刻版。

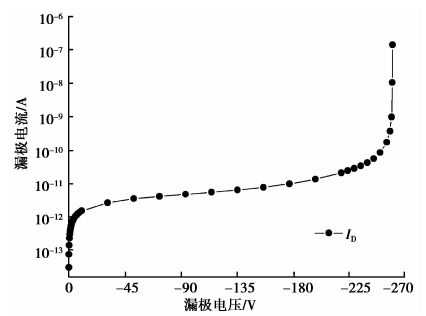

3、 仿真结果分析对于P沟道VDMOS器件,关键的静态参数有3个:击穿电压、导通电阻及阈值电压。其中击穿电压是VDMOS器件有别于普通MOS器件最重要的特性。对元胞的击穿电压的仿真曲线参见图 5,提取BVDS为260.6 V,为器件的终端结构留出了足够余量。

|

图 5 器件元胞击穿曲线 Figure 5 The breakdown voltage curve of designed device |

器件的输出特性曲线如图 6所示,相比于普通的P沟道MOS器件,它有2个明显不同的特点[12]。一是饱和区的输出特性曲线更平(见图 6中A区域),说明其输出阻抗很高,这是因为元胞之间形成相互耗尽,造成使空穴移动的有效漏端电压VD′大幅度降低,当VDS增加时,N阱对电场的屏蔽作用使VD′变化很小;并且此时沟道内空穴速度已经饱和,几乎不随VD′变化,因此在饱和区内ID基本不发生变化。另一个特点是它存在一个明显的准饱和区(Quasi-Saturation region,见图 6中B区域),在该区域内ID随VDS增加,但VGS增加时ID变化极小,这一区域在设计的这种高压VDMOS中表现得尤其明显。其主要原因是在高压VDMOS中,寄生电阻RJFET与REpi阻值很大且串联在漏端,且其阻值将随VDS增加,由于这个串联电阻对VDS的分压作用,使得寄生JFET的导电沟道始终无法夹断,流过寄生JFET的电流不会趋于饱和,但会逼近一个极限。准饱和区使得器件在击穿前的ID始终存在一个极限,并且在准饱和区工作时器件的跨导将会急剧下降,严重限制了器件的性能,因此需要在实际应用中加以留意。

|

图 6 设计器件的输出特性曲线 Figure 6 The output curves of designed device |

通过对P沟道VDMOS器件结构中几个关键因素与性能关系的分析,设计了一款击穿电压超过-200 V、阈值电压-2.78 V的高压大功率P沟道VDMOS器件,利用Atlas对其元胞结构进行了仿真和优化。同时,采用Athena开发了针对该器件的工艺参数和流程。本文的研究结果对项目后续器件的流片提供了有益参考。

| [1] |

张波.功率MOSFET的研究与新发展[C]//2010'全国半导体器件技术研讨会论文集.杭州:半导体技术杂志社, 2010:6-10.

ZHANG Bo.Research and development of power MOSFET[C]//2010'Workshop on National Semiconductor Device Technology.Hangzhou:Semiconductor Technology Magazine, 2010:6-10.(in Chinese)

http://cpfd.cnki.com.cn/article/cpfdtotal-bdth201007001023.htm ( 0) 0)

|

| [2] |

孙伟锋, 张波, 肖胜安, 等.

功率半导体器件与功率集成技术的发展现状及展望[J]. 中国科学(信息科学) , 2012, 42 (12) : 1616–1630.

SUN Weifeng, ZHANG Bo, XIAO Shengan, et al.

Development and trend of power semiconductor devices and power integrated technology[J]. Scientia Sinica (Informationis) , 2012, 42 (12) : 1616–1630.

DOI:10.1360/112012-510 ( 0) 0)

|

| [3] |

Tan Chan-Lik, Strasser M.Improved deep body implant on breakdown voltage in super junction of vertical VDMOS[C]//25th Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA.NY:IEEE, 2014:362-364.

( 0) 0)

|

| [4] |

Liu Siyang, Zhu Rongxia, Jia Kan, et al.

A novel model of the high-voltage VDMOS for the circuit simulation[J]. Solid-State Electronics , 2014, 93 : 21–26.

DOI:10.1016/j.sse.2013.12.006 ( 0) 0)

|

| [5] |

Naugarhiya A, Kondekar P N.Electrical characteristics comparison between process and device structures of super junction VDMOS[C]//IEEE International Conference on Control, Automation, Robotics and Embedded System (CARE):Jabaipur, India.Jabaipur:IEEE, 2013:1-4.

( 0) 0)

|

| [6] |

Sun Weifeng, Zhu Jing, Qian Qingsong, et al.

Trench superjunction VDMOS with charge imbalance cell[J]. Solid-State Electronics , 2011, 64 (1) : 14–17.

DOI:10.1016/j.sse.2011.07.006 ( 0) 0)

|

| [7] |

How P-channel MOSFETs can simplify your circuit[EB/OL].Application Note AN-940.International Rectifier.[2015-12-11].http://www.irf.com/technical-info/appnotes/an-940.pdf..

( 0) 0)

|

| [8] |

蒲石, 郝跃.

一种P沟VDMOS器件的研究与实现[J]. 西安电子科技大学学报 , 2013, 40 (6) : 58–61.

PU Shi, HAO Yue.

The development and realization of P-channel VDMOS[J]. Journal of Xidian University , 2013, 40 (6) : 58–61.

( 0) 0)

|

| [9] |

Baliga B J. Fundamentals of power semiconductor devices[M]. New York: Springer Science Business Media, LLC, 2008 .

( 0) 0)

|

| [10] |

Hu C M, Chi M H, Patel V M.

Optimum design of power MOSFET's[J]. IEEE Transactions on Electron Device , 1984, 31 (12) : 1693–1700.

DOI:10.1109/T-ED.1984.21773 ( 0) 0)

|

| [11] |

Vrej B.Power MOSFET basics[EB/OL].Application Note AN-1084.International Rectifier.[2016-12-11].http://ww.irf.com/technical-info/appnotes/an-1084.pdf.

( 0) 0)

|

| [12] |

陈星弼. 功率MOSFET与高压集成电路[M]. 南京: 东南大学出版社, 1990 .

CHEN Xingbi. Power MOSFET and high voltage integrated circuit[M]. Nanjing: Southeast University Press, 1990 .

( 0) 0)

|

| [13] |

Jiang Wei.Statical simulation and analysis on 650V VDMOS tubes[C]//20132nd International Conference on Measurement, Information and Control (ICMIC):Piscataway, NJ, USA.NJ:IEEE, 2013:1311-1314.

( 0) 0)

|

| [14] |

Zheng Shouguo, Zhang Jian, Zeng Xinhua, et al.Design and process simulation on high voltage VDMOS[M].Advances in Intelligent and Soft Computing, Vol.127:Springer Berlin Heidelberg, 2012:155-164.

https://publications.icd.utt.fr/ ( 0) 0)

|

| [15] |

蒲石, 杜林, 张得玺.

高压P沟道VDMOS的复合耐压终端研究[J]. 西安电子科技大学学报 , 2015, 42 (6) : 84–89.

PU Shi, DU Lin, ZHANG Dexi.

Study on combined edge termination for high voltage P-channel VDMOS[J]. Journal of Xidian University , 2015, 42 (6) : 84–89.

( 0) 0)

|

| [16] |

胡佳贤, 韩雁, 张世峰, 等.高压VDMOS结终端技术研究[C]//2010'全国半导体器件技术研讨会论文集.杭州:半导体技术杂志社, 2010:62-64.

HU Jiaxian, HAN Yan, ZHANG Shifeng, et al.Research on junction termination technique for VDMOSFET[C]//2010'Workshop on National Semiconductor Device Technology.Hangzhou:Semiconductor Technology Magazine, 2010:62-64.(in Chinese)

http://cdmd.cnki.com.cn/article/cdmd-10336-1014230258.htm ( 0) 0)

|

| [17] |

黄京才, 陈骞, 许允亮.

大功率VDMOS (200 V)的设计研究[J]. 现代电子技术 , 2011, 34 (18) : 195–197.

HUANG Jingcai, CHEN Qian, XU Yunliang.

Design of 200 V high power VDMOS[J]. Modern Electronics Technique , 2011, 34 (18) : 195–197.

( 0) 0)

|

| [18] |

孙嘉兴, 宁润涛, 胡子阳, 等.

利用Tsuprem4和Medici对200伏VDMOS进行虚拟制造[J]. 辽宁大学学报 , 2006, 33 (1) : 42–45.

SUN Jiaxing, NING Runtao, HU Ziyang, et al.

Virtual fabrication of 200 volt VDMOS by Tsuprem4 and Medici[J]. Journal of Liaoning University , 2006, 33 (1) : 42–45.

( 0) 0)

|

2016, Vol. 39

2016, Vol. 39